# S P A R C I T Y

### Profiling and instrumentation tools

| Deliverable No:<br>Deliverable Title:<br>Deliverable Publish Date: | D4.1<br>Profiling and instrumentation tools<br>31 March 2022             |

|--------------------------------------------------------------------|--------------------------------------------------------------------------|

| Project Title:                                                     | SPARCITY: An Optimization and Co-design Framework for Sparse Computation |

| Call ID:                                                           | H2020-JTI-EuroHPC-2019-1                                                 |

| Project No:                                                        | 956213                                                                   |

| Project Duration:                                                  | 36 months                                                                |

| Project Start Date:                                                | 1 April 2021                                                             |

| Contact:                                                           | sparcity-project-group@ku.edu.tr                                         |

#### List of partners:

| Participant no. | Participant organisation name                       | Short name | Country  |

|-----------------|-----------------------------------------------------|------------|----------|

| 1 (Coordinator) | Koç University                                      | KU         | Turkey   |

| 2               | Sabancı University                                  | SU         | Turkey   |

| 3               | Simula Research Laboratory AS                       | Simula     | Norway   |

| 4               | Instituto de Engenharia de Sistemas e Computadores, | INESC-ID   | Portugal |

|                 | Investigação e Desenvolvimento em Lisboa            |            |          |

| 5               | Ludwig-Maximilians-Universität München              | LMU        | Germany  |

| 6               | Graphcore AS                                        | Graphcore  | Norway   |

#### CONTENTS

- 1 Introduction 1

- 1.1 Objectives of This Deliverable 1

- 1.2 Work Performed 1

- 1.3 Deviations and Counter Measures 2

- 1.4 Resources 2

#### 2 Performance and energy monitoring events 2

- 2.1 Hardware counters 3

- 2.2 Software events 5

#### 3 Profiling tools based on hardware counters 6

- 3.1 Perf: Performance analysis tools for Linux 6

- 3.2 Performance Application Programming Interface (PAPI) 7

- 3.3 LIKWID performance tools 7

- 4 Communication profiling and monitoring tools 7

- 4.1 ComDetective: A Communication Monitoring Tool 8

- 4.2 ReuseTracker: A Reuse Distance Analysis Tool 9

- 4.3 ComScribe: Inter-GPU Communication Detection Tool 10

5 System-level Monitoring Tools 11

- 5.1 Lightweight Distributed Metric Service (LDMS) 11

- 5.2 Performance Co-Pilot 12

- 5.3 Grafana: Open source visualization tool 12

- 5.4 Measurement Overhead 12

- 6 Dynamic instrumentation and cache partitioning tools 14

- 6.1 Intel SDE, Pin and GTPin 14

- 6.2 Reuse Distance Analysis and Cache Partitioning for the ARM A64FX CPU 15

- 7 Vendor-specific frameworks for application analysis 17

- 7.1 Intel Vtune 18

- 7.1.1 Microarchitectual General Exploration for Intel CPUs 18

- 7.1.2 GPU offload analysis 19

- 7.2 Intel Advisor 20

- 7.3 Profiling and instrumentation on NVIDIA GPUs 22

- 7.4 Tools for visual and programmatic analyses on Graphcore IPUs 24

- 7.4.1 Analysing Poplar Profiles 24

- 7.4.2 Tracing Applications 25

- 8 Cache simulation for irregular memory traffic 25

- 8.1 Cache tracing for sparse matrix-vector multiplication 25

- 8.2 Cache tracing results 27

- 9 Conclusions 30

#### 1 INTRODUCTION

The SPARCITY project is funded by EuroHPC JU (the European High Performance Computing Joint Undertaking) under the 2019 call of Extreme Scale Computing and Data Driven Technologies for research and innovation actions. SPARCITY aims to create a supercomputing framework that will provide efficient algorithms and coherent tools specifically designed for maximizing the performance and energy efficiency of sparse computations on emerging High Performance Computing (HPC) systems, while also opening up new usage areas for sparse computations in data analytics and deep learning.

Sparse computations are commonly found at the heart of many important applications, but at the same time it is challenging to achieve high performance when performing the sparse computations. SPARCITY delivers a coherent collection of innovative algorithms and tools for enabling both high efficiency of sparse computations on emerging hardware platforms. More specifically, the objectives of the project are:

- to develop a comprehensive application and data characterization mechanism for sparse computation based on the state-of-the-art analytical and machine-learning-based performance and energy models,

- to develop advanced node-level static and dynamic code optimizations designed for massive and heterogeneous parallel architectures with complex memory hierarchy for sparse computation,

- to devise topology-aware partitioning algorithms and communication optimizations to boost the efficiency of system-level parallelism,

- to create digital SuperTwins of supercomputers to evaluate and simulate what-if hardware scenarios,

- to demonstrate the effectiveness and usability of the SPARCITY framework by enhancing the computing scale and energy efficiency of challenging real-life applications.

- to deliver a robust, well-supported and documented SPARCITY framework into the hands of computational scientists, data analysts, and deep learning end-users from industry and academia.

#### 1.1 OBJECTIVES OF THIS DELIVERABLE

The objective of this deliverable is to provide an overview of the tools for performance, power and energy monitoring on computing nodes equipped with different device architectures (such as CPU, GPU, and Graphcore IPU), as well as on HPC systems that combine several computing nodes. This step is important in order to define the most adequate platform-specific instrumentation frameworks to be used when assessing the application characteristics, determining the execution bottlenecks and evaluating their ability to fully exploit the capabilities of a given hardware. A special emphasis is paid on tools and frameworks for run-time computation and communication monitoring, also based on hardware counters.

#### 1.2 WORK PERFORMED

In this deliverable, the features of several tools for performance, power and energy monitoring on different computing systems and devices, including multi-core CPUs, GPUs and Graphcore IPUs,

are presented. The deliverable starts with the introduction of some of the existing performance and monitoring events that can be used to profile and identify bottlenecks of sparse applications. Next, a set of profiling tools based on hardware counters is also described, as these tools are traditionally used to access the hardware counters in-built in current computing systems. Since some of these counters can also be used for communication profiling and execution monitoring, these type of tools is also targeted in this deliverable. Moreover, dynamic binary instrumentation approaches are also covered, as the information obtained from these methods can provide additional information to complement the one obtained from hardware and software events. Furthermore, frameworks for application analysis on Intel CPUs and GPUs, NVIDIA GPUs and Graphcore IPUs are also addressed in this deliverable. Finally, a performance model of sparse kernels based on cache simulation is presented.

#### **1.3 DEVIATIONS AND COUNTER MEASURES**

There was no deviation from the work plan.

#### 1.4 **RESOURCES**

It is likely that in the course of the project, new profiling and instrumentation tools and frameworks will be added to the core list provided in this document (and/or their set of features and implementation will be improved).

#### 2 PERFORMANCE AND ENERGY MONITORING EVENTS

Due to the ability of sparse computations to reduce the storage and computational requirements of real-world applications, these type of kernels have become increasingly relevant in several scientific fields, such as physics, mathematics and machine learning.<sup>1</sup> Sparse kernels rely on data formats tailored to efficiently store the non-zero entries of the input data,<sup>2</sup> which result in irregular memory access patterns, leading to performance and efficiency degradation. To tackle this issue, it is essential to correlate the application characteristics and the capabilities of the underlying hardware when performing sparse applications, allowing to uncover the main bottlenecks that affect their execution.

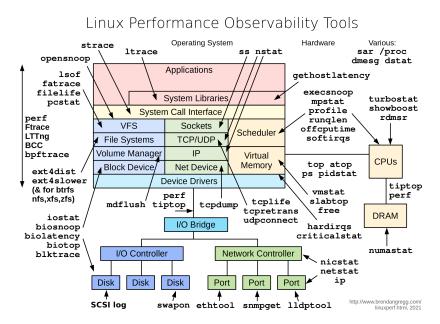

To this end, software and hardware events in-built in current operating and computing systems can be used to to profile application execution on different devices, and to extract metrics useful for the optimization of sparse applications. For example, for the Linux operating system, there are several tools to monitor the different components that compose the operating system (see Figure 1). These software events can provide insights regarding the utilization of different components in the software and hardware stack, *e.g.*, disk and network usages, which can become a bottleneck when deploying sparse applications in large scale systems. Through performance monitoring tools, additional information can be obtained from the hardware counters, which are contained in the chip package of modern processors, thus providing insights on the utilization of different

<sup>&</sup>lt;sup>1</sup>Shail Dave et al. "Hardware Acceleration of Sparse and Irregular Tensor Computations of ML Models: A Survey and Insights". *Proceedings of the IEEE* 109.10 (2021), pp. 1706–1752. DOI: 10.1109/JPROC.2021.3098483; Thaha Mohammed et al. "DIESEL: A novel deep learning-based tool for SpMV computations and solving sparse linear equation systems". *The Journal of Supercomputing* 77.6 (2021), pp. 6313–6355; Amuthan A. Ramabathiran and Prabhu Ramachandran. "SPINN: Sparse, Physics-based, and partially Interpretable Neural Networks for PDEs". *Journal of Computational Physics* 445 (2021), p. 110600. ISSN: 0021-9991. DOI: https://doi.org/10.1016/j.jcp.2021.110600. URL: https://www.sciencedirect.com/science/article/pii/S0021999121004952.

<sup>&</sup>lt;sup>2</sup>Yue Zhao et al. "Bridging the gap between deep learning and sparse matrix format selection". *Proceedings of the* 23rd ACM SIGPLAN symposium on principles and practice of parallel programming. 2018, pp. 94–108.

**Figure 1** *Linux components and specific tools to monitor each component.*<sup>3</sup>

hardware components when performing sparse computations.

#### 2.1 HARDWARE COUNTERS

Modern multi-core CPUs support an extensive set of hardware counters in order to measure events related to the performance and energy consumption of applications, e.g., Intel CPUs provide hundreds of different events that can be tacked.<sup>4</sup> The counters provided by the performance monitoring unit have a vast range of applicability, from measuring the amount of stalls that originate from accessing different hardware components, to the number of floating-point instructions performed by an application, and cache misses that result from each memory level. Since sparse computations are expected to be limited by the memory capabilities of computing devices, mainly due to the irregular accesses, hardware counters related to the memory requests are especially important to profile these workloads. Moreover, counters related to the floating point instructions should also be considered to assess the utilization of compute units. This task can be performed by using the counters presented in Table 1.

When evaluating the accesses to the memory hierarchy, the total amount of loads and stores, and the misses of each level can provide useful insights regarding cache utilization and efficiency of the memory accesses. While for measuring loads, stores and L1 data misses it is only necessary to access a single counter, in the case of L2 cache data misses and L3 misses, it is necessary to obtain data from two counters. In the case of L2 data misses, it is necessary to compute the difference between all the memory requests from the core that reference a cache line in the last level cache (LLC\_REFERENCE) and the code reads that miss L2 cache (L2\_RQSTS.CODE\_RD\_MISS). As for the LLC misses, we rely on the sum of two IMC uncore events,<sup>5</sup> which allow to measure all the access to the main memory, *i.e.*, DRAM reads (CAS\_COUNT\_RD) and DRAM writes (CAS\_COUNT\_WR). Other hardware counters provide

<sup>&</sup>lt;sup>4</sup>R Intel. "and IA-32 Architectures. Software Developer's Manual. Combined Volumes: 1, 2A, 2B, 2C, 3A, 3B and 3C". *Order Number* (64).

<sup>&</sup>lt;sup>5</sup>Intel Xeon Processor Scalable Memory Family. "Uncore Performance Monitoring Reference Manual". *Intel Corporation, July* (2017).

measurements regarding the execution stalls that occur due to the misses in specific memory levels (*e.g.* CYCLE\_ACTIVITY.STALLS\_L1D\_MISS) or regarding the cycles where there are outstanding misses. Given that stalls result in low execution performance and efficiency, considering the measurements obtained from these counters may allow to pinpoint the main execution bottle-necks of sparse computations.

| Metric                               | Hardware Counters                       | Description                                                                                 |

|--------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------------------|

| Cycles                               | CPU_CLK_UNHALTED.THREAD                 | Counts the number of core cycles while the log-                                             |

|                                      |                                         | ical processor is not in halt state.                                                        |

| Loads                                | MEM_INST_RETIRED.ALL_LOADS              | Counts the number of retired loads.                                                         |

| Stores                               | MEM_INST_RETIRED.ALL_STORES             | Counts the number of retired stores.                                                        |

| L1 Data Misses                       | L1D.REPLACEMENT                         | Counts the data line replacements that occur on                                             |

| La Data Missaa                       | LLC DEEEDENICE                          | L1D cache.                                                                                  |

| L2 Data Misses                       | LLC_REFERENCE-<br>L2_RQSTS.CODE_RD_MISS | Number of data requests that miss L2D cache.<br>Corresponds to the difference between every |

|                                      | L2_KQ313.CODE_KD_WII35                  | core request that references a cache line in LLC                                            |

|                                      |                                         | and the L2 code misses.                                                                     |

| LLC Misses                           | CAS_COUNT.RD+CAS_COUNT.WR               | Sum between all DRAM reads and all DRAM                                                     |

|                                      |                                         | writes.                                                                                     |

| L1 Data Stalls                       | CYC_ACT <sup>†</sup> .STALLS_L1D_MISS   | Stalls that occur due to outstanding loads that                                             |

|                                      |                                         | miss L1D cache.                                                                             |

| L2 Stalls                            | CYC_ACT <sup>†</sup> .STALLS_L2_MISS    | Stalls that occur due to outstanding loads that                                             |

|                                      |                                         | miss L2 cache.                                                                              |

| L3 Stalls                            | CYC_ACT <sup>†</sup> .STALLS_L3_MISS    | Stalls that occur due to outstanding loads that                                             |

|                                      |                                         | miss L <sub>3</sub> cache.                                                                  |

| Memory Stalls                        | CYC_ACT <sup>†</sup> .STALLS_MEM_ANY    | Stalls that occur due to outstanding loads in the                                           |

| 5                                    |                                         | memory subsystem.                                                                           |

| Cycles with misses on L1             | CYC_ACT <sup>†</sup> .CYCLES_L1D_MISS   | Cycles while there are outstanding loads that                                               |

| Data                                 |                                         | miss L1D cache.                                                                             |

| Cycles with misses on L2             | CYC_ACT <sup>†</sup> .CYCLES_L2_MISS    | Cycles while there are outstanding loads that                                               |

|                                      |                                         | miss L2cache.                                                                               |

| Cycles with misses on L <sub>3</sub> | CYC_ACT <sup>†</sup> .CYCLES_L3_MISS    | Cycles while there are outstanding loads that                                               |

|                                      |                                         | miss L3 cache.                                                                              |

| Cycles with outstanding              | CYC_ACT <sup>†</sup> .CYCLES_MEM_ANY    | Cycles while there are outstanding loads in the                                             |

| loads                                |                                         | memory subsystem.                                                                           |

| FP Scalar Double                     | FP_AI_RET*.SCALAR_DOUBLE                | Double-precision scalar FP instructions.                                                    |

| FP Scalar Single                     | FP_AI_RET*.SCALAR_SINGLE                | Single-precision scalar FP instructions.                                                    |

| FP 128-bit SIMD Double               | FP_AI_RET*.128B_PACKED_DOUBLE           | Double-precision 128-bit packed FP instruc-                                                 |

| FP 128-bit SIMD Single               | FP_AI_RET*.128B_PACKED_SINGLE           | tions.<br>Single-precision 128-bit packed FP instructions.                                  |

| FP 256-bit SIMD Double               | FP_AI_RET*.256B_PACKED_DOUBLE           | Double-precision 256-bit packed FP instruc-                                                 |

| 11 230-011 011010 DOUDLE             | TI ALLEI .2500-IACKED-DOUDLE            | tions.                                                                                      |

| FP 256-bit SIMD Single               | FP_AI_RET*.256B_PACKED_SINGLE           | Single-precision 256-bit packed FP instructions.                                            |

| FP 512-bit SIMD Double               | FP_AI_RET*.512B_PACKED_DOUBLE           | Double-precision 512-bit packed FP instruc-                                                 |

| -                                    |                                         | tions.                                                                                      |

| FP 512-bit SIMD Single               | FP_AI_RET*.512B_PACKED_SINGLE           | Single-precision 512-bit packed FP instructions.                                            |

| † – CYCLE_ACTIVITY; * – 1            |                                         |                                                                                             |

**Table 1** Hardware counters for profiling sparse computations.

To measure the energy consumption on Intel CPUs, it is necessary to rely on the RAPL interface.<sup>6</sup> As shown in Table 2, RAPL supports different energy domains, each with their specific counter, that can provide different insights about the efficiency of sparse computations. The power plane o (PPo) counter allows to measure the energy from the processor cores and LLC, while the counter from the package domain encapsulates the entire processor package. While the

<sup>&</sup>lt;sup>6</sup>Intel, "and IA-32 Architectures. Software Developer's Manual. Combined Volumes: 1, 2A, 2B, 2C, 3A, 3B and 3C".

package counter is available in all types of Intel processors, the PPo domain is usually specific to client platforms. The power plane 1 (PP1) domain targets the integrated processor graphics in-built on the chip package of the client processors, while the DRAM domain considers the energy consumption of the main memory. Finally, the platform energy counter considers the energy of the cores, integrated graphic, system agent and other hardware components, and it is only available in Skylake or more recent architectures. Its availability also depends on the BIOS support. In case it is not supported in the tested hardware, the counter returns the value of zero.

| Table 2 | Counters supported by RAPL interface. |  |

|---------|---------------------------------------|--|

|---------|---------------------------------------|--|

| Metric               | Hardware Counters           | Description                                      |

|----------------------|-----------------------------|--------------------------------------------------|

| Power Plane o Energy | MSR_PPo_ENERGY_STATUS       | Energy of processor cores and LLC.               |

| Package Energy       | MSR_PKG_ENERGY_STATUS       | Energy of entire processor package.              |

| Power Plane 1 Energy | MSR_PP1_ENERGY_STATUS       | Energy of integrated processor graphics (only    |

|                      |                             | client processors).                              |

| DRAM Energy          | MSR_DRAM_ENERGY_STATUS      | Energy of DRAM (only server processors).         |

| Platform Energy      | MSR_PLATFORM_ENERGY_COUNTER | Energy of entire platform (only if BIOS and ven- |

|                      |                             | dor hardware supports it).                       |

#### 2.2 SOFTWARE EVENTS

Along with hardware events, internal kernel information (vmstat, iostat, disk, network), and process level metrics are also provided by the operating system, e.g., see Figure 1 (taken from<sup>7</sup>). When a (sparse) application runs on a cluster, all of these components can resemble a bottleneck. Hence, by monitoring this information along with the hardware events, spotting performance issues of an application can be possible. Some of these metrics are provided in Table 3.

| Table 3  | Some selected metrics from kernel performance metric counters which could relate to sparse application |

|----------|--------------------------------------------------------------------------------------------------------|

| performa | nce.                                                                                                   |

| Source and Description   | Metric                                | Metric Description                                             |

|--------------------------|---------------------------------------|----------------------------------------------------------------|

|                          | kernel.all.intr                       | Context switches metric from /proc/stat                        |

|                          | kernel.all.pressure.cpu.some.total    | Total time processes stalled for CPU resources                 |

|                          | kernel.all.pressure.memory.some.total | Total time processes stalled for memory re-                    |

| /proc                    |                                       | sources                                                        |

| Kernel statistics        | kernel.all.pressure.memory.full.total | Total time when all tasks stall on memory re-<br>sources       |

|                          | kernel.all.pressure.io.some.total     | Total time processes stalled for IO resources                  |

|                          | kernel.percpu.interrupts.PMI          | Performance monitoring interrupts for each                     |

|                          |                                       | core                                                           |

|                          | kernel.percpu.interrupts.TRM          | Thermal event interrupts for each core                         |

|                          | kernel.percpu.interrupts.line*        | Number of interrupts caused by each IO device                  |

|                          | mem.util.used                         | Used system memory                                             |

|                          | mem.util.free                         | Free system memory                                             |

| /proc/meminfo            | mem.util.directMap4k                  | Amount of memory that is directly mapped in 4kB pages          |

| System memory statistics | mem.util.directMap2M                  | Amount of memory that is directly mapped in 2MB pages          |

|                          | mem.util.directMap1G                  | Amount of memory that is directly mapped in 1GB pages          |

|                          | swap.pagesin                          | Pages read from swap devices due to demand for physical memory |

<sup>&</sup>lt;sup>7</sup>Brendan Gregg. 2021. URL: https://brendangregg.com/linuxperf.html.

|                              | swap.pagesout                                  | Pages written to swap devices due to demand                     |

|------------------------------|------------------------------------------------|-----------------------------------------------------------------|

|                              |                                                | for physical memory                                             |

|                              | mem.numa.util.free                             | Per-node free memory                                            |

|                              | mem.numa.util.used                             | Per-node used memory                                            |

| /proc/meminfo                | mem.numa.alloc.hit                             | Per-node count of times a task wanted alloc on                  |

| NUMA statistics              |                                                | local node and succeeded                                        |

|                              | mem.numa.alloc.miss                            | Per-node count of times a task wanted alloc on                  |

|                              |                                                | local node but got another node                                 |

|                              | mem.numa.alloc.local_node                      | Per-node count of times a process ran on this                   |

|                              |                                                | node and got memory on this node                                |

|                              | mem.numa.alloc.other_node                      | Per-node count of times a process ran on this                   |

|                              |                                                | node and got memory on another node                             |

| /proc/vmstat                 | mv <sup>†</sup> .kswapd_low_wmark_hit_quickly  | Count of times low watermark reached quickly                    |

| Virtual memory statistics    | mv <sup>†</sup> .kswapd_high_wmark_hit_quickly | Count of times high watermark reached quickly                   |

| /proc/net/dev                | network.interface.in.bytes                     | Network recv read bytes per network interface                   |

| Network interface statistics | network.interface.out.bytes                    | Network send bytes per network interface                        |

|                              | disk.dev.read                                  | Per-disk read operations                                        |

| /proc/diskstats              | disk.dev.write                                 | Per-disk write operations                                       |

| Disk statistics              | disk.dev.read_merge                            | Per-disk count of merged read requests                          |

|                              | disk.dev.write_merge                           | Per-disk count of merged write requests                         |

|                              | proc.psinfo.ngid                               | NUMA group identifier                                           |

|                              | proc.psinfo.threads                            | Number of threads                                               |

|                              | proc.psinfo.nvctxsw                            | Number of non-voluntary context switches                        |

| /proc/ <pid>/*</pid>         | proc.psinfo.processor                          | Last CPU the process was running on                             |

| Per process statistics       | proc.psinfo.cmaj_flt                           | Count of page faults other than reclaims of all exited children |

|                              | proc.psinfo.maj_flt                            | Count of page faults other than reclaims                        |

|                              | proc.io.wchar                                  | write(), writev() and sendfile() send bytes                     |

|                              | proc.io.rchar                                  | read(), readv() and sendfile() receive bytes                    |

| <sup>†</sup> – mem.vmstat    |                                                | · · · · · ·                                                     |

#### 3 PROFILING TOOLS BASED ON HARDWARE COUNTERS

The access to the hardware counters and the energy counters supported by the RAPL interface on Intel devices, it is usually required to have privileged access, thus they cannot be accessed from user space. To overcome this issue and to to ease the adoption of counters for profiling applications and modeling computing systems, monitoring tools, such as, Perf,<sup>8</sup> PAPI,<sup>9</sup> and LIKWID,<sup>10</sup> can be used to easily configure and access the counters. All these tools allow to access both the hardware counters for performance monitoring and the RAPL interface when targeting the energy consumption of a system.

#### 3.1 PERF: PERFORMANCE ANALYSIS TOOLS FOR LINUX

Perf is included in the Linux kernel and relies on a command line interface to configure the hardware counters and performing the measurements. This tool not only supports hardware counters, but also tracepoints, kprobes and uprobes for dynamic tracing. To simply profile the entire execution of an application, *perf stat* command must be used. Moreover, the event accounts can also be recorded through the command *perf record*, which together with the commands *perf*

<sup>&</sup>lt;sup>8</sup>Arnaldo Carvalho De Melo. "The new linux'perf'tools". *Slides from Linux Kongress*. Vol. 18. 2010, pp. 1–42.

<sup>&</sup>lt;sup>9</sup>Dan Terpstra et al. "Collecting performance data with PAPI-C". *Tools for High Performance Computing* 2009. Springer, 2010, pp. 157–173.

<sup>&</sup>lt;sup>10</sup>J. Treibig, G. Hager, and G. Wellein. "LIKWID: A lightweight performance-oriented tool suite for x86 multicore environments". *Proceedings of PSTI2010, the First International Workshop on Parallel Software Tools and Tool Infrastructures*. 2010.

*report* and *perf annotate* allow to breakdown the measured events by process/function and/or to annotate the application source code with the event counts. This allows to detect which application kernels should be the focus for optimization. Besides these features, perf also allows to print the sampled functions in real time (*perf top*), as well as to perform different multi-threaded micro-benchmarks to evalute the capabilities of CPU devices (*perf bench*).

#### 3.2 PERFORMANCE APPLICATION PROGRAMMING INTERFACE (PAPI)

PAPI profiles applications or specific regions of interest by manually inserting functions/markers in the application code. When using PAPI, the first step is to initialize the PAPI library (*PAPI\_library\_init*). When targeting multi-thread applications, it is also necessary to initialize the PAPI interface for multiple threads (*PAPI\_thread\_init*). After initializing PAPI, the second step is to select the counters to be read by each thread/core. This needs to be explicitly performed by the programmer in the application code, through the functions *PAPI\_create\_eventset* and *PAPI\_add\_event* to create a event set and add counters to it. The list of events supported by the computing system can be obtained from the executable files *papi\_avail* and/or *papi\_native\_avail*. After adding the events to measure to the event set, the counting of the hardware counters must be started with *PAPI\_start*. After starting the counting, to profile specific application kernels, *PAPI\_read* calls can be inserted around the region of interest to read the current values of the hardware counters. Finally, at the end of the application code, the counting of the hardware counters must be stopped (*PAPI\_stop*) and the envent set cleaned (*PAPI\_cleanup\_eventset*) and destroyed (*PAPI\_destroy\_eventset*).

#### 3.3 LIKWID PERFORMANCE TOOLS

LIKWID is another alternative to Perf and PAPI. Similar to Perf, it allows to profile the entire application execution by using a command line interface (*likwid-perfctr*). This interface is also responsible to select and configure the hardware counters. However, LIKWID also includes a mechanism to profile specific regions of the application, by relying on the marker API. The first step is to initialize the LIKWID marker interface (*LIKWID\_MARKER\_INIT*). In the case of multi-thread applications, it is also necessary to call the function *LIKWID\_MARKER\_THREADINIT*. After this initialization step, the *LIKWID\_MARKER\_START* and *LIKWID\_MARKER\_STOP* must be placed before and after the region of interest. To reduce the overhead when performing the measurements, the user can attribute names to the different regions and register them before starting the measurements (*LIKWID\_MARKER\_REGISTER*). Finally, at the end of the application the LIKWID marker interface must be closed (LIKWID\_MARKER\_CLOSE). With this approach, the values obtained for each hardware event and in each core are presented in a command line output.

#### 4 COMMUNICATION PROFILING AND MONITORING TOOLS

Communication is one of the main factor that prevents parallel applications from scaling to large number of cores. In the context of multi-threaded applications, data movement or communication takes place in forms of cache line transfers across multiple cores within or across sockets. Because of the criticality of communication in the performance of an application, in the SPARCITY project, we leverage communication monitoring tools developed by the KU partner. These tools are

namely ComDetective,<sup>11</sup> ReuseTracker<sup>12</sup> and ComScribe.<sup>13</sup> All these three tools are publicly available on the ParCoreLab git repository: https://github.com/ParCoreLab/ParCoreTools

#### 4.1 COMDETECTIVE: A COMMUNICATION MONITORING TOOL

Inter-thread data movement is a vital performance indicator in multi-core systems. To detect inter-thread communications in multi-threaded codes with low time and memory overheads, the KU partner previously developed ComDetective,<sup>14</sup> a tool that captures inter-thread communications in the forms of communication matrices. The tool employs hardware performance counters (PMUs) to sample memory-access events and uses hardware debug registers to capture communicating pairs of threads. A PMU is a special on-chip hardware in each CPU core that can be used to monitor hardware events, such as memory loads, stores etc, or software events like page faults, while a debug register is a special register that can be programmed to monitor any memory address and trap the next access to that memory address.

ComDetective works by sampling memory accesses in each application thread using PMUs and publishing the sampled memory addresses on a global data structure called BulletinBoard. In addition to publishing sampled addresses to BulletinBoard, each sampling thread also attempts to detect inter-thread communication by comparing the cache lines of its sampled addresses with the cache lines of the addresses published on BulletinBoard. If there is a matching cache line, a communication is detected, otherwise, one address in BulletinBoard posted by another thread is randomly selected and its cache line is monitored by the debug registers in the currently sampling thread to trap a communication.

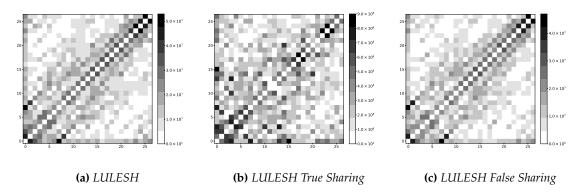

In addition to detecting communications, ComDetective also differentiates the communications into true sharing and false sharing. This can be useful for the application users if they would like to eliminate or reduce false sharing in their codes by making data structure changes. Furthermore, it also attributes the detected communications to their locations in source code and the data objects involved in the communications.

This tool works in both Intel and AMD architectures. To ensure precision of event sampling, it leverages Processor Event-Based Sampling (PEBS)<sup>15</sup> in Intel and Instruction-Based Sampling (IBS)<sup>16</sup> in AMD. The group's work on extending the tool to ARM-based multicore architectures is in progress.

The KU partner verified the accuracy of ComDetective using several microbenchmarks<sup>17</sup> that have known ground truths. These benchmarks were designed to have known ground truths for total number of communications, ratio of false sharing to true sharing, and distribution of communication volume across communicating thread pairs. The communications captured

<sup>&</sup>lt;sup>11</sup>Muhammad Aditya Sasongko et al. "ComDetective: A Lightweight Communication Detection Tool for Threads". *Proceedings of the International Conference for High Performance Computing, Networking, Storage and Analysis.* Denver, Colorado: Association for Computing Machinery, 2019. DOI: 10.1145/3295500.3356214. URL: https://doi.org/10.1145/3295500.3356214.

<sup>&</sup>lt;sup>12</sup>Muhammad Aditya Sasongko et al. "ReuseTracker: Fast Yet Accurate Multicore Reuse Distance Analyzer". *ACM Trans. Archit. Code Optim.* 19.1 (2021). ISSN: 1544-3566. DOI: 10.1145/3484199. URL: https://doi.org/10.1145/3484199.

<sup>&</sup>lt;sup>13</sup>Palwisha Akhtar et al. "ComScribe: Identifying Intra-node GPU Communication". 2021. DOI: 10.1007/978-3-030-71058-3\_10.

<sup>&</sup>lt;sup>14</sup>Sasongko et al., "ComDetective: A Lightweight Communication Detection Tool for Threads".

<sup>&</sup>lt;sup>15</sup>Intel. Intel Microarchitecture Codename Nehalem Performance Monitoring Unit Programming Guide. https://software. intel.com/sites/default/files/m/5/2/c/f/1/30320-Nehalem-PMU-Programming-Guide-Core.pdf. 2010.

<sup>&</sup>lt;sup>16</sup>Paul J. Drongowski. Instruction-Based Sampling: A New Performance Analysis Technique for AMD Family 10h Processors. https://pdfs.semanticscholar.org/5219/4b43b8385ce39b2b08ecd409c753e0efafe5.pdf. 2007.

<sup>&</sup>lt;sup>17</sup>Sasongko et al., "ComDetective: A Lightweight Communication Detection Tool for Threads".

**Figure 2** Communication matrices of LULESH (Left to Right: All, True and False Sharing). Darker color indicates more communication.

by ComDetective from these benchmarks are close to these ground truths. Moreover, the KU partner also evaluated the time and memory overheads of ComDetective by running it on twelve PARSEC<sup>18</sup> and six CORAL benchmarks<sup>19202122232425</sup> in an Intel Broadwell machine. Figure 2 shows the communication matrices from LULESH, one of the CORAL benchmarks. Its average overheads are 1.30× for runtime and 1.27× for memory overheads under 500K sampling interval, which are much lower than the overheads of cycle-accurate simulators<sup>262728</sup> and prior-art code instrumentation tools<sup>2930</sup>.<sup>31</sup>

#### 4.2 REUSETRACKER: A REUSE DISTANCE ANALYSIS TOOL

Data locality is another important performance indicator in multi-core machines with multi-level caches. One widely used metric that measures data locality is reuse distance, which calculates the number of unique memory locations accessed between two memory accesses to a particular

<sup>&</sup>lt;sup>18</sup>C. Bienia et al. "The PARSEC benchmark suite: Characterization and architectural implications". 2008 International Conference on Parallel Architectures and Compilation Techniques (PACT). 2008, pp. 72–81.

<sup>&</sup>lt;sup>19</sup>AMG. Parallel Algebraic Multigrid Solver. https://github.com/LLNL/AMG. 2017.

<sup>&</sup>lt;sup>20</sup>Ulrike Meier Yang. "Parallel Algebraic Multigrid Methods High Performance Preconditioner". Numerical Solution of Partial Differential Equations on Parallel Computers, LNCS 51 (2006), pp. 209–233.

<sup>&</sup>lt;sup>21</sup>Quicksilver. A proxy app for the Monte Carlo Transport Code, Mercury. https://github.com/LLNL/Quicksilver.

<sup>&</sup>lt;sup>22</sup>PENNANT. Unstructured mesh hydrodynamics for advanced architectures. https://github.com/lanl/PENNANT. 2016. <sup>23</sup>miniFE. MiniFE Finite Element Mini-Application. https://github.com/Mantevo/miniFE.

<sup>&</sup>lt;sup>24</sup>VPIC. Vector Particle-In-Cell (VPIC) Project. https://github.com/lanl/vpic.

<sup>&</sup>lt;sup>25</sup>LULESH 2.0. Livermore Unstructured Lagrangian Explicit Shock Hydrodynamics (LULESH). https://github.com/ LLNL/LULESH.

<sup>&</sup>lt;sup>26</sup>Nick Barrow-Williams, Christian Fensch, and Simon Moore. "A communication characterisation of Splash-2 and Parsec". *IEEE International Symposium on Workload Characterization*, 2009. *IISWC* 2009. 2009.

<sup>&</sup>lt;sup>27</sup>P.S. Magnusson et al. "Simics: A full system simulation platform". Computer 35.2 (2002), pp. 50–58.

<sup>&</sup>lt;sup>28</sup>Eduardo Henrique Molina da Cruz et al. "Using Memory Access Traces to Map Threads and Data on Hierarchical Multi-core Platforms". 2011 IEEE International Symposium on Parallel and Distributed Processing Workshops and Phd Forum (IPDPSW). 2011.

<sup>&</sup>lt;sup>29</sup>Matthias Diener et al. "Characterizing communication and page usage of parallel applications for thread and data mapping". *Performance Evaluation* 88-89 (2015), pp. 18–36.

<sup>&</sup>lt;sup>30</sup>Arya Mazaheri, Felix Wolf, and Ali Jannesari. "Characterizing Loop-Level Communication Patterns in Shared Memory Applications". *Proceedings of the 2015 44th International Conference on Parallel Processing*. Beijing, China, 2015. DOI: 10.1109/ICPP.2015.85.

<sup>&</sup>lt;sup>31</sup>Arya Mazaheri, Felix Wolf, and Ali Jannesari. "Unveiling Thread Communication Bottlenecks Using Hardware-Independent Metrics". *Proceedings of the 47th International Conference on Parallel Processing*. Eugene, OR, USA: ACM, 2018, 6:1–6:10. DOI: 10.1145/3225058.3225142. URL: http://doi.acm.org/10.1145/3225058.3225142.

memory location. To profile reuse distance in multi-threaded code with low runtime and memory overheads, the KU partner developed ReuseTracker.<sup>32</sup> This profiling tool leverages PMUs to sample memory accesses and uses debug registers to detect either a *reuse* or a cache line invalidation of the sampled memory location. ReuseTracker works in Intel by leveraging PEBS and in AMD by leveraging IBS. Similar to ComDetective, its extension to ARM-based multicore architectures is in progress.

ReuseTracker employs two different algorithms that profile reuse distance in private caches and shared caches, respectively. To profile reuse distance in private caches, each thread that encounters a PMU sample arms a debug register in every CPU core in the machine. If the next debug register trap occurs in the same CPU core as the PMU sample, a reuse in private cache is detected, otherwise, if the next trap happens in another core, a cache line invalidation at private cache level is detected. When a reuse is detected, the number of memory accesses between the PMU sample and the debug register trap is recorded into a time reuse distance histogram, which is then converted into stack reuse distance histogram using the method in.<sup>33</sup> In the algorithm that profiles reuse distance in shared caches, each thread that faces a PMU sample arms a debug register in every other core in the machine. A reuse in the same shared cache is detected if the next trap happens in another core that shares the same socket, and a cache line invalidation at shared cache level is detected when the next trap occurs in another core located in another socket. When a reuse at shared cache level is detected, the number of memory accesses in all cores that share the same socket is recorded in the time reuse distance histogram.

To evaluate the accuracy of ReuseTracker, the KU partner developed a microbenchmark that can be configured to generate a variety of reuse distance patterns. The private cache profiling algorithm has been evaluated on this microbenchmark, and its accuracy is 92% in an Intel Skylake machine under 100K sampling interval. The overheads of this tool have also been evaluated by running it on ten PARSEC benchmarks with  $2.9 \times$  runtime and  $2.8 \times$  memory overheads under the same sampling interval, which are much lower than the overheads of the other open source reuse distance analysis tools.<sup>34</sup>

#### 4.3 COMSCRIBE: INTER-GPU COMMUNICATION DETECTION TOOL

Communication monitoring among GPUs can help reason about scalability issues and performance divergence between different implementations of the same application. ComScribe<sup>35</sup> is a tool that can identify communication among all GPU-GPU and CPU-GPU pairs in a single-node multi-GPU system. It can monitor data movement induced by both Peer-to-Peer (P2P) primitives of CUDA and collective communication primitives of NVIDIA's Collective Communication Library (NCCL). It employs the NVIDIA's profiling tool nvprof and Unix dynamic linker utility to monitor P2P communication and collective communication respectively to gather the necessary information. Then, the collected information is processed to quantify communication among GPUs and generate the communication matrices. In the SPARCITY project, we plan to leverage this tool to monitor inter-GPU communication in multi-GPU applications with this tool.

<sup>&</sup>lt;sup>32</sup>Sasongko et al., "ReuseTracker: Fast Yet Accurate Multicore Reuse Distance Analyzer".

<sup>&</sup>lt;sup>33</sup>Xipeng Shen, Jonathan Shaw, and Brian Meeker. "Accurate Approximation of Locality from Time Distance Histograms". 2006.

<sup>&</sup>lt;sup>34</sup>Xiaoya Xiang et al. "HOTL: A Higher Order Theory of Locality". SIGARCH Comput. Archit. News 41.1 (2013), pp. 343–356. ISSN: 0163-5964. DOI: 10.1145/2490301.2451153. URL: https://doi.org/10.1145/2490301.2451153; dcompiler/loca: Program locality analysis tools. https://github.com/dcompiler/loca.

<sup>&</sup>lt;sup>35</sup>Akhtar et al., "ComScribe: Identifying Intra-node GPU Communication".

#### **5 SYSTEM-LEVEL MONITORING TOOLS**

In order to systematically collect and store information from performance metric sources, several monitoring tools are developed and widely used in the literature. These tools aim to provide a wider picture on the system performance via monitoring multiple components of and building relations among them. These systems are used to facilitate intelligent job placement, run-time workload partitioning/adaptation and HPC hardware procurement planning.<sup>36</sup> Some of these tools are: LDMS,<sup>37</sup> Performance Co-Pilot,<sup>38</sup> Ganglia,<sup>39</sup> Nagios, HPC-Toolkit<sup>40</sup> and PerfAugur.<sup>41</sup> Among them Ganglia is proven to be scalable up to 2000 nodes but is used for general system monitoring, requires considerable number of installation dependencies, targets larger collection intervals (10s of seconds to 10s of minutes) and uses an aging tool for storage. Nagios also targets larger collection intervals (10s of seconds to 10s of minutes) and mainly used for failure alerts. PerfAugur is used to trace the cause of a system anomaly by finding common attributes that predicate an anomaly.<sup>42</sup> HPCToolkit is a suite of tools which can provide accurate measurements of program performance on a wide variety of systems from single host computers to large clusters. However it involves a binary analysis and re-compilation of the target code. LDMS and Performance Co-Pilot are metric collection, transport and storage systems which can be configured to sample every performance metric counter on hardware and kernel including RAPL, PAPI and perf interfaces. Moreover they support frequent and variable sampling rate on these performance metrics with negligible overhead and without requirement of recompile or source code instrumentation. This enables real time monitoring of HPC systems in cluster level, node level and process level in order to provide multiple-aspect insight of application performance.

#### 5.1 LIGHTWEIGHT DISTRIBUTED METRIC SERVICE (LDMS)

LDMS is part of OVIS, a suite of HPC monitoring, analysis and feedback tools which is jointly developed by Sandia National Laboratories and Open Grid Computing. LDMS is based on daemons called 1dmsd which can run on either sampler or aggregator modes. A sampler 1dmsd daemon is created by running and configuring sampling plugins which sample PMUs. Each sampling plugin combines a specific set of data into a single metric set. An aggregator 1dmsd daemon is created by running and 1dsmd and configuring aggregator plugings. Each aggregator collect metric sets from samplers and/or other aggregators. Higher level aggregators can listen many lower level aggregators, aggregate and streams data into storage. LDMS can store sampled performance data on CSV files, D-SOS and InfluxDB. Increasing with number of sampled metrics, LDMS causes very little overhead on the system performance. It causes  $\approx 0.01\%$  CPU utilization,

<sup>&</sup>lt;sup>36</sup>James M. Brandt, Thomas Tucker, and Ann C. Gentile. *Lightweight Distributed Metric Service (LDMS): Run-time Resource Utilization Monitoring*. English. Tech. rep. SAND2013-6521C. Sandia National Lab. (SNL-CA), Livermore, CA (United States); Sandia National Lab. (SNL-NM), Albuquerque, NM (United States), 2013. URL: https://www.osti.gov/biblio/1106397 (visited on 09/27/2021).

<sup>&</sup>lt;sup>37</sup>Anthony Michael Agelastos et al. *The Lightweight Distributed Metric Service: A Scalable Infrastructure for Continuous Monitoring of Large Scale Computing Systems and Applications.* English. Tech. rep. SAND2014-19868C. Sandia National Lab. (SNL-NM), Albuquerque, NM (United States); Sandia National Lab. (SNL-CA), Livermore, CA (United States), 2014. DOI: 10.1109/SC.2014.18. URL: https://www.osti.gov/biblio/1315267 (visited on 09/27/2021).

<sup>&</sup>lt;sup>38</sup>Red-Hat. URL: https://pcp.io/.

<sup>&</sup>lt;sup>39</sup>Ganglia. Ganglia monitoring system. URL: http://ganglia.sourceforge.net/.

<sup>&</sup>lt;sup>40</sup>L. Adhianto et al. "HPCTOOLKIT: Tools for Performance Analysis of Optimized Parallel Programs Http://Hpctoolkit.Org". *Concurr. Comput.: Pract. Exper.* 22.6 (2010), pp. 685–701. ISSN: 1532-0626.

<sup>&</sup>lt;sup>41</sup>Sudip Roy et al. "PerfAugur: Robust diagnostics for performance anomalies in cloud services". 2015 IEEE 31st International Conference on Data Engineering. 2015, pp. 1167–1178. DOI: 10.1109/ICDE.2015.7113365.

<sup>&</sup>lt;sup>42</sup>Agelastos et al., *The Lightweight Distributed Metric Service*.

<2MB memory, <4MB filesystem and 4KB network overhead for  $\approx200$  metrics @1 second intervals.^43

Although it has been widely used in the literature, and it works well under certain circumstances, LDMS is mostly used by a strictly related group, lacks documentation and still under development. Therefore it's hard to deploy, develop and maintain.

#### 5.2 PERFORMANCE CO-PILOT

Performance Co-Pilot, which was initially released at 1995 by SCI and currently being developed by Red-Hat is a system performance analysis toolkit. PCP contains two types of components: PCP collectors and PCP monitors. PCP collectors are responsible for collecting and extracting performance data from various sources. This sources could be PMCs, PMUs or application performance logs. PCP collectors consists of two components; Performance Metrics Domain Agent (PMDA) and Performance Metric Collector Daemon (PMCD). PMDAs connects to performance sources and sample their values, then reports these values to PMCD. There currently 75 PMDAs available and apart from existing PMDAs, new PMDAs could be developed to connect any wanted performance metrics source using PMAPI library. To be able to report metrics from a host machine, there must be a PMCD which listen and control all PMDAs and answer requests of monitoring applications. Monitoring tools are used to display, manipulate and store performance metrics extracted from PMCDs. PMCDs can collect performance metrics from remote hosts or answer to remote monitoring tools in a distributed setting. Some of the PCP monitoring tools are; PMIE, an inference engine which could be used to automate system management tasks via predicate-action rules. PMLOGGER, archive manager which enables subsets of collected performance metrics to be replayed. PMCHART, a visualization tool which can generate on the fly charts from collected metrics. PMREP, a performance metrics reporter with highly customizable output format. PCP can export collected metrics to several databases such as; Elasticsearch, Graphite, InfluxDB, Redis and Apache Spark.

#### 5.3 GRAFANA: OPEN SOURCE VISUALIZATION TOOL

Grafana is an open source visualization tool which provides dynamic dashboards, ad-hoc queries and alerting functions on time-series data. Since it's initial release at 2014, Grafana quickly become industry standard and reached 10M+ global users recently. Due to it's massive userbase, Grafana provides support for every popular database and provides a wide variety of visualization methods. Due to it's strong recognition and flexibility, Grafana is chosen as Digital SuperTwin front-end interface during development in order to prove usability of design concepts for Digital SuperTwin's own interface.

#### 5.4 MEASUREMENT OVERHEAD

The overhead for a default configuration of Performance Co-Pilot is reported in Table 4. Since the default configurations of monitoring tools focused on overall system health and component state, main effort is put on reconfiguration of sampler processes to sample performance centric metricsets and development of custom samplers. On top of that, to be able to implement and test customized solutions for monitoring and to report reproducible results, a freely available research medium is required. To this end, virtual clusters using docker containers as compute node, which can perform MPI communications and managed by SLURM is realized. But since this framework is still under development, results acquired from this setting, along with the custom samplers and

<sup>&</sup>lt;sup>43</sup>Agelastos et al., The Lightweight Distributed Metric Service.

**Figure 3** An example Grafana dashboard showing performance metrics collected by PCP and indexed with InfluxDB on a single host. Exhibiting node-level monitoring usage.

**Figure 4** An example Grafana dashboard showing statistics for processes used for creating Table 3. Exhibiting process-level monitoring usage.

implementation of monitoring tool on physical clusters will be reported at the next deliverable.

| Sampler / Reporter      | pcp2influxdb | pmcd | pmdaroot | proc_pmda | xfs_pmda | linux_pmda | perfevent_pmda |

|-------------------------|--------------|------|----------|-----------|----------|------------|----------------|

| CPU Percentage          | 19.1         | 0.1  | 0.1      | 7.3       | 0.09     | 1.6        | 0.1            |

| Resident Set Size (MBs) | 46.7         | 4.4  | 3.8      | 6.3       | 3.6      | 5.7        | 7.6            |

**Table 4** Overhead of Performance Co-Pilot agents on a single host machine with default installation. Among 2857 metrics collected by samplers, 107 are reported to InfluxDB. Average CPU usage and RSS of processes for one hour is reported.

#### **6 DYNAMIC INSTRUMENTATION AND CACHE**

#### PARTITIONING TOOLS

Hardware counters are extremely useful to extract metrics to understand the behavior of applications in current computing systems. However, they do not encapsulate all the information about the specifics of an application. For example, while the hardware counters on Intel CPUs allow to count the number of retired loads and stores, they do not provide information related to the size each memory access. Similarly, while there are counters for floating-point operations, no information can be inferred for integer operations. Both these specifics can be crucial when understanding the bottlenecks of sparse computations, as well as to achieve accurate application characterization.<sup>44</sup> To overcome these issues, dynamic instruction tools can be used to dynamically evaluate the instructions executed by the application to obtain profile regarding the type of instructions performed.

#### 6.1 INTEL SDE, PIN AND GTPIN

For Intel CPUs, one of the most known tools is the Intel Software Development Emulator (SDE).<sup>45</sup> Intel SDE is a emulation tool built on top of Intel Pin,<sup>46</sup> which allows to debug programs using instructions before their release. Intel SDE also contains a histogram tool, which can be used to dynamically count the instructions executed by an application. This can be divided according to their ISA extension, type, data size, etc. Since the instrumentation is performed while Intel SDE discovers the execution path of the application, the results obtained are more reliable than the ones obtained by statically analyse the assembly code. Intel SDE also supports a marker API to only obtain the dynamic trace of specific applications kernels, by placing the \_\_SSC\_MARK macros around the code. Given that Intel SDE is able to categorize memory and compute instructions in different categories, *e.g.*, according to their size and data type, this tool can also be fundamental when applying specific modeling approaches, such as roofline modeling methodologies.

The binary instrumentation can also be performed on Intel GPUs by relying on GTPin,<sup>47</sup> an adaptation of the Intel Pin to Intel GPU architectures. GTPin features a binary instrumentation engine for the execution units in Intel GPUs, a set of sample tools and an API for developing additional analysis tools. GTPin instrumentation can be used to gather data for workloads in compute and graphics applications, enabling fast analysis of code running in the GPU. GTPin capabilities are used in various profiling tools, such as Intel Profiling Tools Interface for GPU,<sup>48</sup>

<sup>&</sup>lt;sup>44</sup>Diogo Marques et al. "Application-driven cache-aware roofline model". *Future Generation Computer Systems* 107 (2020), pp. 257–273.

<sup>&</sup>lt;sup>45</sup>Moshe Bach et al. "Analyzing parallel programs with pin". Computer 43.3 (2010), pp. 34–41.

<sup>&</sup>lt;sup>46</sup>Chi-Keung Luk et al. "Pin: building customized program analysis tools with dynamic instrumentation". *Acm sigplan notices* 40.6 (2005), pp. 190–200.

<sup>&</sup>lt;sup>47</sup>Intel Corporation. *GTPin*. https://software.intel.com/sites/landingpage/gtpin/index.html. [Online; visited March-2022].

<sup>&</sup>lt;sup>48</sup>Intel Corporation. *Profiling Tools Interfaces for GPU (PTI for GPU)*. https://github.com/intel/pti-gpu. [Online; visited March-2022].

Intel Advisor and Intel VTune. It is supported in both integrated and discrete Intel GPUs.

## 6.2 REUSE DISTANCE ANALYSIS AND CACHE PARTITIONING FOR THE ARM A64FX CPU

Due to high costs incurred when accessing main memory, data locality is an important consideration when optimizing numerical kernels. Caches keep small amounts of data close to the processor's compute units, and thus have the potential to speed up computation and reduce energy consumption. Programmers may exploit caches by employing optimization techniques such as blocking or tiling. To ease programmability, the cache is automatically managed by hardware and its contents are under implicit but not explicit control of a programmer. The implicit control a programmer may enact is imprecise and has limitations, because CPU hardware is complex, several subsystems may be interacting unpredictably and the precise functionality of these subsystems is often not documented.

*Cache partitioning* is an approach to give programmers significantly more explicit control over cache functionality. It allows the available cache space to be divided into a configurable number of partitions. Data structures (corresponding to one or more address ranges) may be assigned to a dedicated partition. This is especially promising in situations where data is repeatedly accessed and should be retained in cache but is evicted by intervening unrelated data accesses due to the cache's eviction policy (typically a variant of LRU - least recently used). In a partitioned cache each partition is managed with a separate eviction policy and by assigning the reusable data its own partition it can be shielded from evection by the unrelated data accesses.

A feature for cache partitioning as described above is not available in most mainstream CPUs but has been available in the SPARC64VIIIfx CPU<sup>49</sup> developed by Fujitsu for the K computer system and has also been introduced in the Fujitsu A64FX CPU powering the Fugaku system (#1 in the Top 500 list as of November 2021). In the A64FX CPU the feature is called *instruction-based way partitioning* and referred to as the *sector cache*. It works by dividing the "ways" dimension of the 4-way set-associative L1 data cache or 16-way set-associative L2 cache into two or more sectors. An extension to the Fujitsu compiler suite can be used to specify which data structures should be assigned to a dedicated sector.

While a potentially powerful feature, unless a developer knows an application's data reuse pattern in great detail, it will be a challenge to determine whether cache partitioning may be a profitable option and which data structures to isolate in dedicated sectors. To help developers with these questions, a tool was developed at LMU Munich<sup>50</sup> which can be used to derive hints about a sector cache configuration and identify candidate data structures to assign a dedicated sector. The tool works by monitoring and analysing the accessed memory locations during execution to compute reuse distance histograms under various hypothetical partitioning scenarios.

The tool is based on dynamic binary instrumentation using Intel Pin<sup>51</sup> and captures memory accesses during execution. Based on the stream of accessed memory locations, reuse distance histograms are computed. The reuse distance of a memory access for a particular location is the number of distinct memory locations referenced since the last access to this same location. The reuse distances can then be aggregated per data structure into reuse distance histograms, and these histograms can be used to derive hints about which data structures may benefit from a placement in a dedicated sector. If the reuse distances of a data structure are predominantely

<sup>&</sup>lt;sup>49</sup>Toshio Yoshida et al. "SPARC64 VIIIfx: CPU for the K computer". Fujitsu Sci. Tech. J 48.3 (2012), pp. 274–279.

<sup>&</sup>lt;sup>50</sup>Sergej Breiter. "Evaluating Sector Caches in High-Performance Computing". Master Thesis. Ludwig-Maximilians-Universität München, 2022.

<sup>&</sup>lt;sup>51</sup>Luk et al., "Pin: building customized program analysis tools with dynamic instrumentation".

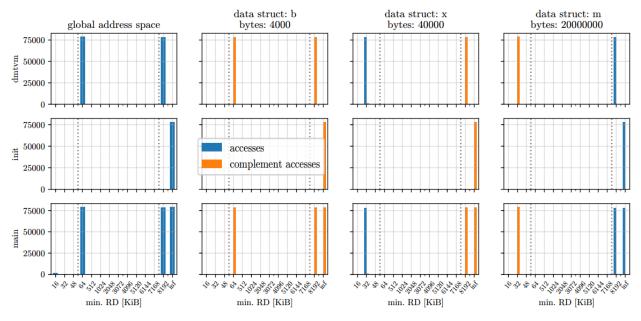

Figure 5 Reuse distance histograms of the DMTVM data structure.

| region | data struct | cache level | nways | misses sc | misses nosc | reduction [%] |

|--------|-------------|-------------|-------|-----------|-------------|---------------|

| main   | m           | 1           | 1     | 156824    | 236875      | 33.79         |

| main   | m           | 2           | 2     | 156583    | 157742      | 0.73          |

| dmtvm  | m           | 1           | 1     | 78447     | 157277      | 50.12         |

| dmtvm  | m           | 2           | 2     | 78237     | 78450       | 0.27          |

**Figure 6** The tool's output of the sector cache configuration for DMTVM. The number of L1D cache misses can be reduced significantly by isolating m in the function dmtvm in a partition with quota of one cache way.

larger than the capacity of a cache, LRU implies that data is evicted just before being reused. By using two partitions, the reuse distance histogram is split into two histograms in which the main amount of accesses may now be smaller than the partition's size, thereby providing a benefit.

As an example for how the tool can be used, Fig.5 shows the output for the simple dmtvm (Dense Matrix Transposed Vector Multiplication) benchmark application. The source code consists of the *main* function, the *init* function and the *dmtvm* kernel itself, which is shown in Fig 7. The multiplication operates on the input matrix m, the multiplicand vector b and stores the result in the vector x. x is reused in every row of the multiplication, m is streamed and never reused and b can be ignored regarding memory accesses, because only one element of b is loaded per row. m interferes with the reuse of x and doubles the reuse distances of accesses to x, because equal amounts of data from x and m are required during the calculation of each row.

In the reuse distance histograms shown in Fig. 5, the number of the double precision floatingpoint matrix rows is set to 500 and the number of columns is set to 5000. This leads to the sizes of 4KB for b, 40KB for x and 20MB for m. Thus, x can fit in 3 ways of the L1D cache (total size 64 KB) and m does not fit in the L2 cache (total size 8 MB). In the main function (third row of histograms), accesses to the global address space (first column) have only reuse distances higher than the L1D capacity. The accesses with reuse distance 8 are attributable to the init function (second row) and are compulsory misses. Accesses with other reuse distances occur during the

```

#pragma scache_isolate_way L1=1

#pragma scache_isolate_assign m

#pragma omp for

for ( int i = o ; i < nrow ; ++i ) {

for ( int j = o ; j < ncol ; ++j ) {

x[j] += m[i * ncol + j] * b[i] ;

}}</pre>

```

**Figure 7** Dense Matrix Transposed Vector Multiplication (dmtvm) source code and example sector cache configuration using Fujitsu compiler directives, called Optimization Control Lines (OCLs).

multiplication (first row). Isolating b (second column) does not change the reuse distances and can be omitted as option. Isolating x (third column) shifts the reuse distances of accesses to x (blue) below the L1D capacity. Other accesses (orange) are not negatively affected. This is exactly as expected, because x is reused frequently and 40KB large. The isolation of m (fourth column) shifts the reuse distances of accesses to its complementary data structure below the L1D cache capacity.

The output of the analysis is shown in Fig. 6. The optimal sector cache configuration is the isolation of m in the smallest possible sector of each cache level which halves the L1D misses when applied. This is again as expected, because half of the accesses are made to x which can be reused when it is isolated from the interfering accesses to m. Isolating m in a small sector slightly decreases the cache misses compared to isolating x in a sector of appropriate size, because it has a minor positive affect on the reuse of b.

The predicted configuration has been tested on a Fujitsu A64FX system installed at the Leibniz Supercomputing Center (LRZ) and the measurements of the L1D and L2 misses on the A64FX CPU have been found to be in line with the predictions of the tool. The measured L2 misses in the dmtvm function remained unchanged at around 80000 when the sector cache was applied. On the other hand, the measured L1D misses went down from 142000 to 81000. Similar results can be observed for the L2 cache partitioning.

#### 7 VENDOR-SPECIFIC FRAMEWORKS FOR APPLICATION

#### ANALYSIS

Another approach to evaluate the execution of applications in current computing systems is the utilization of frameworks provided by the different vendors. For example, for Intel CPUs and GPUs, Intel Advisor can be used to obtain metrics related to the instruction mix, memory accesses and execution time, together with the Cache-Aware Roofline Model,<sup>52</sup> which is proposed by the INESC-ID partner and fully automated in this framework. Intel Vtune also encapsulates the Top-Down method,<sup>53</sup> which provides an extensive evaluation of the application execution to identify which hardware resources are limiting application performance. For NVIDIA GPUs, similar information can be obtained from the NVIDIA Visual Profile,<sup>54</sup> while the PopVision and Poplar tools can be used to analyze applications running in Graphcore IPU systems.

<sup>&</sup>lt;sup>52</sup>Marques et al., "Application-driven cache-aware roofline model".

<sup>&</sup>lt;sup>53</sup>Ahmad Yasin. "A top-down method for performance analysis and counters architecture". 2014 IEEE International Symposium on Performance Analysis of Systems and Software (ISPASS). IEEE. 2014, pp. 35–44.

<sup>&</sup>lt;sup>54</sup>NVIDIA Corporation. *Profiler User's Guide*. NVIDIA Corporation. 2022. URL: https://docs.nvidia.com/cuda/profiler-users-guide/index.html.

#### 7.1 INTEL VTUNE

Intel VTune Profiler is a framework developed by Intel that provides different methods for application analysis on CPUs, GPUs and FPGAs. With the information provided by Intel VTune, it is possible to optimize application performance on diverse systems. In this deliverable, we focus on two main approaches included in Intel VTune, namely: the Microarchitectual General Exploration<sup>55</sup> for Intel CPU applications, and the GPU offload analysis for workloads deployed on Intel GPUs. Microarchitectual General Exploration can be used to identify bottlenecks related to the different hardware components on the CPU architecture/system, by using hardware counters to pinpoint the performance issues. The GPU offload analysis supports DPC++ and OpenCL kernels and provides several performance metrics that allow to verify the parallelism efficiency of the application.

#### 7.1.1 MICROARCHITECTUAL GENERAL EXPLORATION FOR INTEL CPUS

In a simplistic view, execution bottlenecks on current computing devices can be either attributed to the maximum performance limits of specific units or due to micro-architectural stalls. The Top-Down analysis<sup>56</sup> focuses on these aspects, identifying if in a given cycle the pipeline slots are empty or filled with a micro-operation ( $\mu op$ ). This modeling method is integrated in Intel VTune, under the Microarchitectual Exploration analysis.<sup>57</sup> This analysis provides several metrics in respect to different parts of the micro-architecture and are derived by relying on the performance monitoring unit in-built in Intel processors. For this analysis, the events are collected in the Event-Based Sampling (EBS) mode. With EBS, each hardware counter is configured to provide a sample-after-value and once this value is reached, the counter increments, an interrupt is fired and the data collected. After data collection, the counter is reset and the process is repeated. Moreover, in recent micro-architectures, the Microarchitectual Exploration analysis collects around 60 hardware events. Since there is a limited number of hardware counters to use simultaneously, Intel VTune relies on multiplexing to obtain all the measurements in a single profiling run, which can reduce the accuracy of the analysis, especially for short lived kernels. To overcome this issue, multiple runs can be performed at the cost of higher profiling overhead. While the sampling methodology of Microarchitectual Exploration analysis allows it to characterize different hotspots of an application, by attributing the different samples to the loops and functions of an application, this analysis can also be applied to specific regions of interest through the use of the marker API, by placing \_\_itt\_resume() and \_\_itt\_pause() calls around the code region to profile.

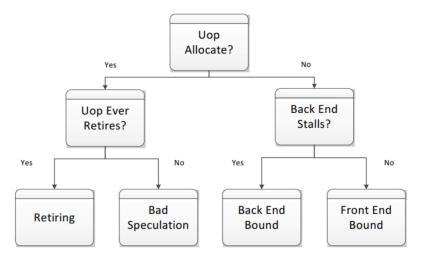

As it can be observed in Figure 8, the Top-Down method integrated in Intel VTune is based on a hierarchical tree organization. In the scenario that the pipeline slot is empty, it is necessary to identify if the stall occurs due to the instruction fetching and decoding (frontend) or due to the availability of the data operands (backend). On the other hand, in case the pipeline slot contains a  $\mu$ op, the bottleneck can be either due to the retiring limits of the architecture (usually 4  $\mu$ op on Intel processors) or due to the branch prediction engine (bad speculation). Depending on the identified bottleneck, different insights can be derived. For example, when an application is limited by the frontend, the user must focus on improving the code layout or reduce the code memory footprint. Issues related to bad speculation indicate that the code must be inspected to avoid indirect branches or error conditions that result in machine clears. Since the branch

<sup>&</sup>lt;sup>55</sup>Intel Corporation. Understanding How General Exploration Works in Intel<sup>®</sup> VTune<sup>™</sup> Amplifier. https://www.intel. com/content/www/us/en/developer/articles/technical/understanding-how-general-exploration-works-inintel-vtune-amplifier-xe.html. [Online; visited March-2022].

<sup>&</sup>lt;sup>56</sup>Yasin, "A top-down method for performance analysis and counters architecture".

<sup>&</sup>lt;sup>57</sup>Intel Corporation, Understanding How General Exploration Works in Intel<sup>®</sup> VTune<sup>™</sup> Amplifier.

Figure 8 Hierarchical organization of Top-Down analysis<sup>58</sup>

prediction engine also influences the fetched instructions, reducing the bad speculation issues may also decrease the impact of the frontend bottlenecks. When an application is limited by retiring, it means that most of its µops are being executed at the maximum throughput of the micro-architecture. However, this does not mean that the performance of the application is maximized. For example, if a scalar application is entirely limited by retiring, vectorization techniques must be employed to further improve performance. Finally, backend issues can be either a result of core bound stalls or memory bound stalls. Core bound stalls can occur when certain execution units are not fully utilized or when there is competition for discrete execution units. Memory bound stalls result from accesses to the memory hierarchy, such as cache misses or latency-related issues, which is expected to be the main source of bottlenecks when profiling sparse computations. The memory bound stalls are further split according to each memory level contained in the memory hierarchy: L1 bound, L2 bound, L3 bound and DRAM bound. From each of the metrics it is also possible to identify if the performance issues result from latency or bandwidth, as well as other inefficiencies, such as false sharing at the L3 cache when executing in multiple-threads.

#### 7.1.2 GPU OFFLOAD ANALYSIS

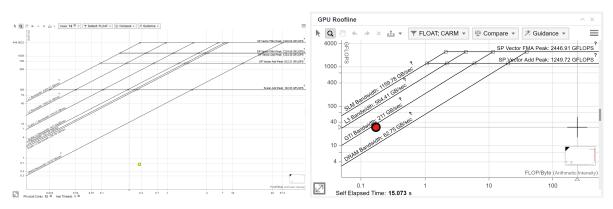

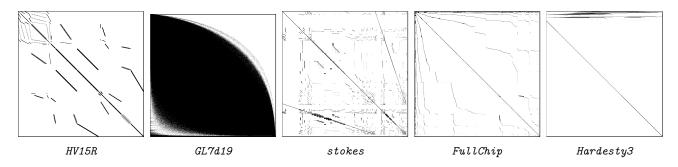

The primary analysis type in VTune used for GPU applications is the GPU Offload analysis. It allows to explore the application execution in the current platform consisting on CPU and GPU, correlate the activity in both devices, and identify if the application's performance is bounded by the CPU or GPU. For compute applications using DPC++ or OpenCL kernels, it allows to explore the efficiency of the application when using GPU hardware.