# Prototype of performance and energy models

| Deliverable No:<br>Deliverable Title:<br>Deliverable Publish Date: | D1.2<br>Prototype of performance and energy models<br>30 June 2022       |

|--------------------------------------------------------------------|--------------------------------------------------------------------------|

| Project Title:                                                     | SPARCITY: An Optimization and Co-design Framework for Sparse Computation |

| Call ID:                                                           | H2020-JTI-EuroHPC-2019-1                                                 |

| Project No:                                                        | 956213                                                                   |

| Project Duration:                                                  | 36 months                                                                |

| Project Start Date:                                                | 1 April 2021                                                             |

| Contact:                                                           | sparcity-project-group@ku.edu.tr                                         |

# List of partners:

| Participant no. | Participant organisation name                       | Short name | Country  |

|-----------------|-----------------------------------------------------|------------|----------|

| 1 (Coordinator) | Koç University                                      | KU         | Turkey   |

| 2               | Sabancı University                                  | SU         | Turkey   |

| 3               | Simula Research Laboratory AS                       | Simula     | Norway   |

| 4               | Instituto de Engenharia de Sistemas e Computadores, | INESC-ID   | Portugal |

|                 | Investigação e Desenvolvimento em Lisboa            |            |          |

| 5               | Ludwig-Maximilians-Universität München              | LMU        | Germany  |

| 6               | Graphcore AS                                        | Graphcore  | Norway   |

# CONTENTS

- 1 Introduction 1

- 1.1 Objectives of This Deliverable 1

- 1.2 Work Performed 2

- 1.3 Deviations and Counter Measures 2

- 1.4 Resources 2

- 2 Sparse-aware roofline modeling and analysis 3

- 2.1 Analysis of sparse kernels in Original Roofline Model 5

- 2.1.1 Sparse matrix-vector multiplication 5

- 2.1.2 Original Roofline Model Analysis 5

- 2.2 Sparse CARM: Improving roofline insightfulness for sparse computations 8

- 2.2.1 Adapting CARM to SpMV 9

- 2.2.2 Impact of sparse matrix characteristics in Sparse CARM 12

- 2.2.3 Improving SpMV performance by reordering 13

- 2.3 Mansard Roofline Model: Sparse Kernels Analysis 23

- 2.3.1 Mansard Roofline Model 23

- 2.3.2 Characterization of Sparse Kernels 29

- 2.3.3 Case Study: Second-Order Epistasis Detection 32

- 3 Performance and Energy-efficiency Modeling of Graphcore Intelligent Processing Unit 35

- 3.1 Roofline modeling of the in-tile execution 35

- 3.2 Modeling Impact of Inter-Tile Communication: Exchange phase 38

- 3.3 Roadmap for IPU Roofline development 40

- 4 Data Movement Analysis 41

- 4.1 Inter-Thread Communication Analysis 41

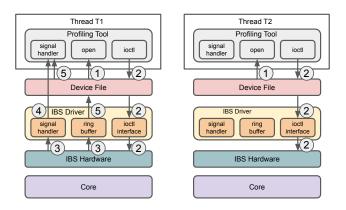

- 4.1.1 ComDetective 41

- 4.1.2 Implementation 42

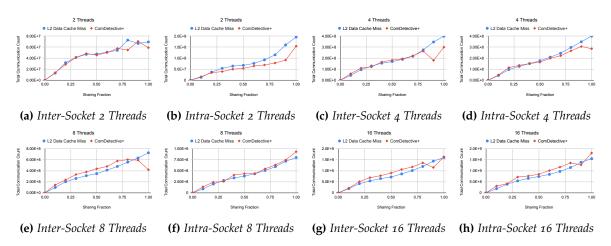

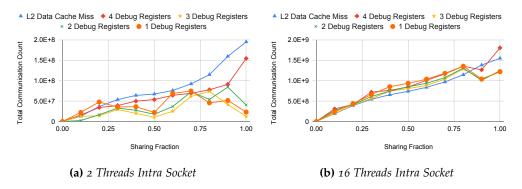

- 4.1.3 Communication Count Analysis 44

- 4.1.4 ComDetective<sup>+</sup> Roadmap 46

- 4.2 Cache Partitioning 46

- 4.2.1 Profiling Tool 47

- 4.2.2 Results 47

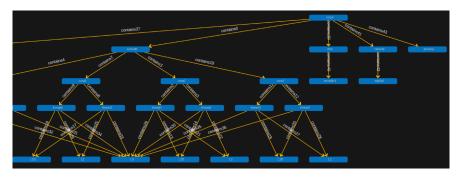

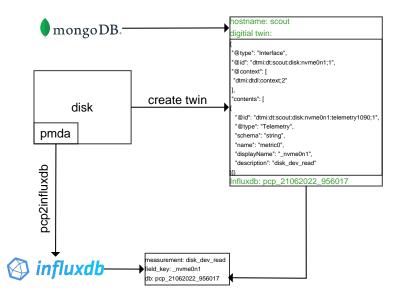

- 5 Digital SuperTwin 48

- 5.1 Probing 49

- 5.2 Constructing Digital Twin 49

- 5.3 Digital SuperTwin Roadmap 51

- 6 Conclusions 52

# 1 INTRODUCTION

The SPARCITY project is funded by EuroHPC JU (the European High Performance Computing Joint Undertaking) under the 2019 call of Extreme Scale Computing and Data Driven Technologies for research and innovation actions. SPARCITY aims to create a supercomputing framework that will provide efficient algorithms and coherent tools specifically designed for maximizing the performance and energy efficiency of sparse computations on emerging High Performance Computing (HPC) systems, while also opening up new usage areas for sparse computations in data analytics and deep learning.

Sparse computations are commonly found at the heart of many important applications, but at the same time it is challenging to achieve high performance when performing the sparse computations. SPARCITY delivers a coherent collection of innovative algorithms and tools for enabling both high efficiency of sparse computations on emerging hardware platforms. More specifically, the objectives of the project are:

- to develop a comprehensive application and data characterization mechanism for sparse computation based on the state-of-the-art analytical and machine-learning-based performance and energy models,

- to develop advanced node-level static and dynamic code optimizations designed for massive and heterogeneous parallel architectures with complex memory hierarchy for sparse computation,

- to devise topology-aware partitioning algorithms and communication optimizations to boost the efficiency of system-level parallelism,

- to create digital SuperTwins of supercomputers to evaluate and simulate what-if hardware scenarios,

- to demonstrate the effectiveness and usability of the SPARCITY framework by enhancing the computing scale and energy efficiency of challenging real-life applications.

- to deliver a robust, well-supported and documented SPARCITY framework into the hands of computational scientists, data analysts, and deep learning end-users from industry and academia.

# 1.1 OBJECTIVES OF THIS DELIVERABLE

The objective of this deliverable is to document the ongoing research developments regarding the sparse computation-aware performance and energy-efficiency modeling of device architectures along with analysis/profiling tools. These models aim at encapsulating necessary information regarding the performance and energy-efficiency upper-bounds that are realistically exploitable by different classes of sparse applications, thus they can be used to guide optimizations and detect the potential execution bottlenecks with respect to compute and memory resources (e.g., caches and DRAM). In addition, communication modeling and analysis tools aim at identifying horizontal and vertical data movement within the memory hierarchy. The data movement profiling information enables us to optimize communication, data placement and cache partitioning. Finally, the developed performance, communication and energy models provide feedback to the Digital Twin to construct unified models.

### **1.2 WORK PERFORMED**

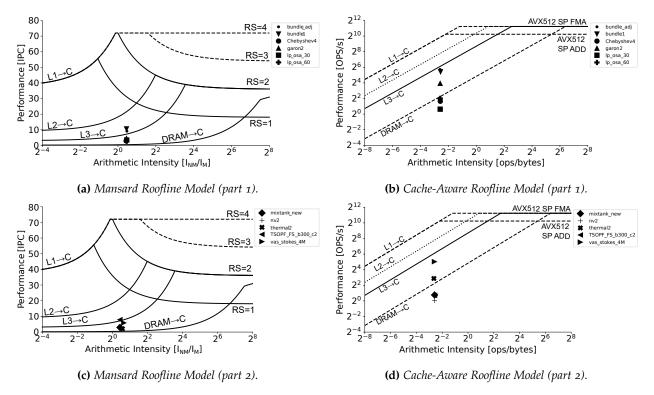

In this deliverable, an extensive analysis, validation and characterization of different sparse computation kernels was performed in the state-of-the-art insightful models based on the roofline principles, in particular, in the Original Roofline Model (ORM) and Cache-aware Roofline Model (CARM). For this purpose, sparse matrices from SuiteSparse Matrix Collection with different sparsity patterns and characteristics were evaluated, across a set of custom-build algorithms and standard implementations from vendor-specific high-performance libraries, including Sparse Matrix-Vector Multiplication (SpMV) and Sparse Matrix-Matrix Multiplication (SpMM) from Intel MKL. A novel ORM analysis based on best- and worst case memory traffic estimates is also derived. A methodology based on micro-benchmarking is proposed to improve the CARM insightfulness by scaling the performance upper-bounds according to the characteristics of the sparse kernels. The proposed model is experimentally evaluated by considering different reordering algorithms applied to diverse sparse matrices in single- and multi-core execution scenarios.

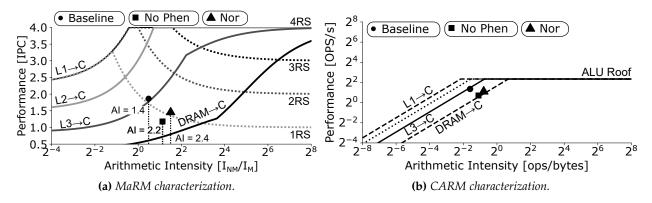

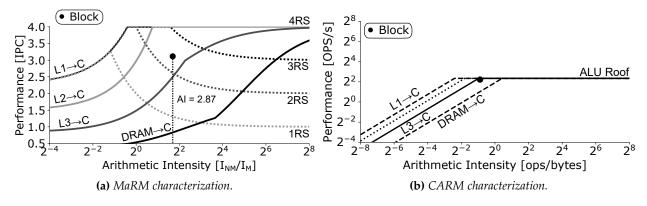

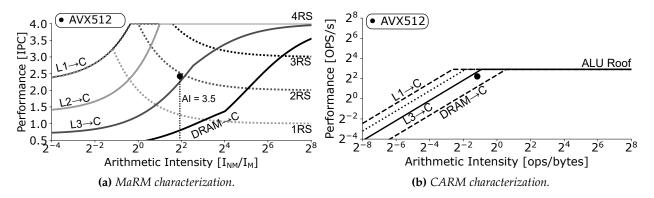

Furthermore, to address the main drawbacks of the SoA roofline models, the Mansard Roofline Model (MaRM) is proposed, which uncovers a minimum set of architectural features that must be considered to provide insightful, but yet accurate and realistic, modeling of performance upper bounds for modern processors. This model encapsulates the retirement constraints due to the amount of retirement slots, Reorder-Buffer and Physical Register File sizes, and it is employed to characterize SpMV and SpMM kernels from Intel MKL, as well as to guide the optimization of the second-order epistasis detection algorithm (use-case application in the scope of the SparCity project). The obtained results show that the characterization in the proposed models is in line with the Intel TopDown VTune analysis.

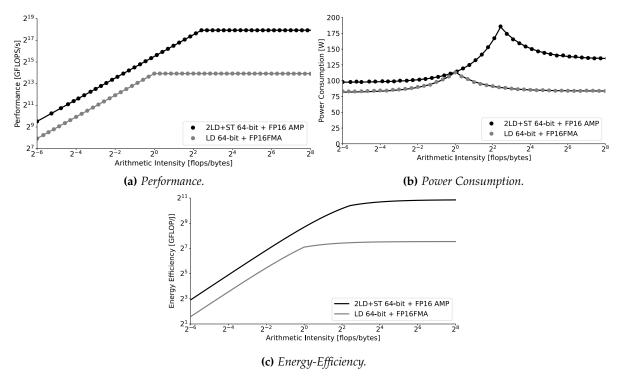

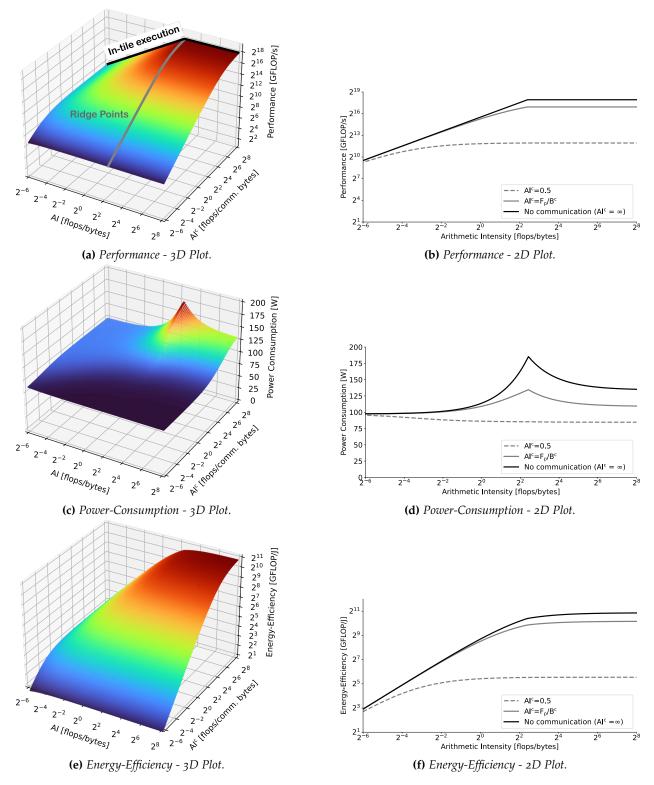

Moreover, the roofline modeling principles are also applied when uncovering the performance and energy-efficiency upper-bounds of the Graphcore Intelligent Processing Unit (IPU). For this purpose, different strategies are considered to model different phases of the IPU execution, i.e., in-tile execution and inter-tile communication (exchange). The proposed in-tile execution roofline model is experimentally validated through micro-benhmarking, which shows complete matching between the theoretical model and the experimental data in all modeled domains, i.e., performance, power consumption and energy-efficiency.

In terms of data movement tools, the inter-thread communication detection tool is extended to AMD x86 architectures and tested on a number of benchmarks for its accuracy, sensitivity to sampling interval and time/memory overheads. Moreover, cache partitioning is applied to an iterative conjugate gradient method based on a CSR SpMV kernel to reduce L2 cache misses. The initial results show that even though the matrices that are already reordered for optimal cache reuse can still benefit from cache partitioning to further reduce cache misses. Lastly, all the performance, power and communication models developed in this WP are communicated to the WP4 team to influence the design of performance metrics in Digital Twin.

# **1.3 DEVIATIONS AND COUNTER MEASURES**

There was no deviation from the work plan.

#### 1.4 **RESOURCES**

As also envisioned in the project proposal, it is expected that the herein elaborated modeling approaches will undergo further improvements and developments, which will be reported in subsequent deliverables (D4.2, D1.4 and D1.5), as well as maintained and regularly updated on the respective SPARCITY Github repositories.

# 2 SPARSE-AWARE ROOFLINE MODELING AND ANALYSIS

The State-of-the-Art (SoA) roofline models, such as, Original Roofline Model (ORM)<sup>1</sup> and its hierarchical variant,<sup>2</sup> Integrated Roofline Model (IRM),<sup>3</sup> and Cache-Aware Roofline Model (CARM)<sup>4</sup> are widely used for application characterization and optimization, especially when considering sparse computations.<sup>5</sup> The popularity of these models arise from their ability to relate application behavior and device upper-bounds in a simple and insightful way. These models focus on the peak compute performance and maximum achievable memory bandwidth, which provides a visualization of the main bottlenecks that hinder application execution, and its potential to fully explore system capabilities.

In particular, CARM characterizes performance upper-bounds for a given architecture, with respect to the arithmetic intensity (AI), *i.e.*, the amount of performed computations over the total amount of requested data (bytes).<sup>6</sup> By considering that memory operations and computations can be simultaneously executed in modern out-of-order processors, the overall execution is limited either by the time to perform computations or by the time to serve memory requests. Hence, CARM contains three distinct regions: memory bound region (slanted roof), compute bound region (horizontal roof) and a "mixed" region, where applications can be both memory and/or compute bound. For each memory level, the slanted roof intersects the horizontal roof at a single point, *i.e.*, the ridge point.<sup>7</sup>

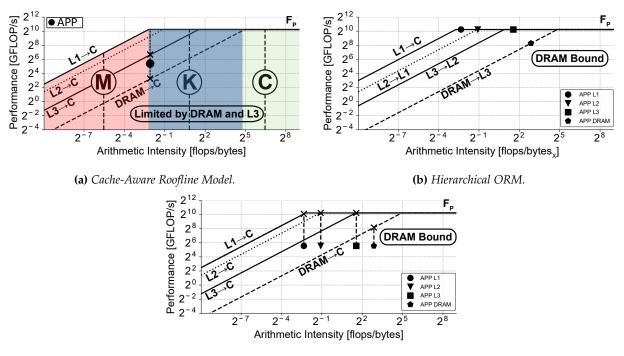

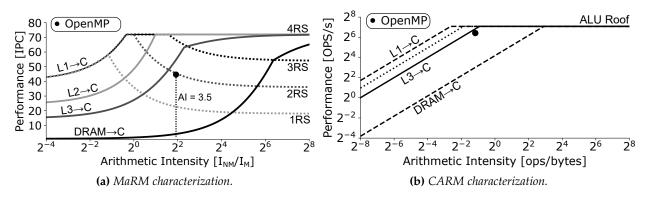

As it can be observed in Figure 1a, CARM memory region includes all memory levels (L1, L2, L3 and DRAM) in a single plot, each limited by its corresponding slanted roof. The maximum attainable performance in this region is limited by the L1 cache bandwidth, while the remaining levels offer a lower attainable performance, due to the reduction in the sustainable bandwidth when data is fetched further away from the core. The right part of the model, delimited by the maximum FP performance ( $F_p$ ), represents the compute bound region.

When characterizing the application behavior, CARM decouples the bottlenecks limiting the application execution, allowing to select suitable optimization techniques to be applied. For example, if an application is at the left side of the ridge point (kernel "M" in Figure 1a), its execution is limited by memory accesses and can be improved by applying memory-related optimizations. On the other hand, an application positioned at the right side of the ridge point (kernel "C" in Figure 1a) is limited by arithmetic operations and its execution can be improved by

<sup>&</sup>lt;sup>1</sup>Samuel Williams, Andrew Waterman, and David Patterson. "Roofline: An Insightful Visual Performance Model for Multicore Architectures". *Commun. ACM* 52.4 (2009), pp. 65–76. ISSN: 0001-0782. DOI: 10.1145/1498765.1498785.

<sup>&</sup>lt;sup>2</sup>Douglas Doerfler et al. "Applying the roofline performance model to the Intel Xeon Phi Knights Landing processor". *Proceedings of the International Conference on High Performance Computing*. Springer. 2016, pp. 339–353.

<sup>&</sup>lt;sup>3</sup>Tuomas Koskela et al. "A novel multi-level integrated Roofline model approach for performance characterization". *Proceedings of the International Conference on High Performance Computing*. Springer. 2018, pp. 226–245.

<sup>&</sup>lt;sup>4</sup>Aleksandar Ilic, Frederico Pratas, and Leonel Sousa. "Cache-aware Roofline model: Upgrading the loft". *IEEE Computer Architecture Letters* 13.1 (2013), pp. 21–24; Diogo Marques et al. "Performance analysis with Cache-Aware Roofline model in Intel Advisor". *Proceedings of the International Conference on High Performance Computing & Simulation*. IEEE. 2017, pp. 898–907.

<sup>&</sup>lt;sup>5</sup>N. Srivastava et al. "MatRaptor: A Sparse-Sparse Matrix Multiplication Accelerator Based on Row-Wise Product". 2020 53rd Annual IEEE/ACM International Symposium on Microarchitecture (MICRO). 2020, pp. 766–780. DOI: 10.1109/ MICRO50266.2020.00068; N. Srivastava et al. "Tensaurus: A Versatile Accelerator for Mixed Sparse-Dense Tensor Computations". 2020 IEEE International Symposium on High Performance Computer Architecture (HPCA). 2020, pp. 689– 702. DOI: 10.1109/HPCA47549.2020.00062; Jiajia Li et al. "A Sparse Tensor Benchmark Suite for CPUs and GPUs". 2020 IEEE International Symposium on Workload Characterization (IISWC). IEEE. 2020, pp. 193–204.

<sup>&</sup>lt;sup>6</sup>Ilic, Pratas, and Sousa, "Cache-aware Roofline model: Upgrading the loft".

<sup>&</sup>lt;sup>7</sup>Ilic, Pratas, and Sousa, "Cache-aware Roofline model: Upgrading the loft"; Aleksandar Ilic, Frederico Pratas, and Leonel Sousa. "Beyond the Roofline: Cache-Aware Power and Energy-Efficiency Modeling for Multi-Cores". *IEEE Transactions on Computers* 66.1 (2016), pp. 52–58.

(c) Integrated Roofline Model.

**Figure 1** *State-of-the-art Roofline Modeling approaches.*

code vectorization or parallelization. Finally, an application placed in the "mixed" region (kernel "K" in Figure 1a) may be limited by computations and/or memory transfers, depending on their instruction mix and on the memory levels exercised by the application.

Moreover, by plotting a vertical line at the AI of the application, as shown in Figure 1a, it is possible to uncover the main sources of performance degradation. The intersections of this vertical line and the CARM roofs represent the potential execution bottlenecks that might limit application performance. The intersections right above and below the application point are identified as the main sources of performance degradation and should be the main target of optimization. In the example of Figure 1a, the main bottlenecks of the application are accesses to L3 and DRAM memories (see black dot in Figure 1a).

Compared to ORM and IRM, while the compute region is evaluated equally in all three models, their modeling of the upper-bounds in the memory subsystem differs. Hierarchical ORM (Figure 1b) considers the bandwidth between memory levels, and its AI corresponds to the amount of performed computations over the amount of data requested by memory level "x" (bytes<sub>x</sub>).<sup>8</sup> Due to this property, a single application (kernel) is represented by "x" points in Hierarchical ORM, one for each memory level. Similar to CARM, the memory region of the Hierarchical ORM contains several roofs, each one representing a memory level. The main execution bottleneck corresponds to the minimum of the intersections between the AIs of the "x" points with their correspondent roofs (*e.g.*, DRAM bandwidth in Figure 1b). Finally, IRM (Figure 1c) uses the modeling approach of CARM in the memory subsystem *i.e.*, it considers the sustainable bandwidth seen from the core for each memory level, while adopting ORM methodology for application characterization and bottleneck detection (*e.g.*, in Figure 1c, DRAM is the main execution bottleneck).

<sup>&</sup>lt;sup>8</sup>Williams, Waterman, and Patterson, "Roofline: An Insightful Visual Performance Model for Multicore Architectures".

### 2.1 ANALYSIS OF SPARSE KERNELS IN ORIGINAL ROOFLINE MODEL

Performance models such as the Original Roofline Model (ORM)<sup>9</sup> are often used to describe the upper limits of achievable performance for computational kernels on a particular hardware. While such models are simple and effective, they sometimes fail to predict the performance that is observed in practice, especially in the case of kernels that are dominated by irregular memory accesses. More detailed performance models are therefore being explored in the context of the SPARCITY project, precisely because irregular memory access patterns are an inherent feature of the kind of sparse computations that SPARCITY is aimed at. One such detailed performance model has been recently developed based on a cache tracing approach.<sup>10</sup> This has so far been applied to better understand the performance of irregular kernels, in particular different variants of Sparse Matrix Vector Multiplication (SpMV).

This section briefly describes a common sparse matrix-vector multiplication kernel and an ORM analysis based on best- and worst case memory traffic estimates. The shortcomings of this simple model illustrates the need for more detailed approaches.

#### 2.1.1 SPARSE MATRIX-VECTOR MULTIPLICATION

A commonly used sparse matrix-vector multiplication kernel based on the compressed sparse row (CSR) storage format is shown in Algorithm 1. This kernel computes  $\mathbf{y} \leftarrow \mathbf{y} + \mathbf{A}\mathbf{x}$ , or

$$y_{i} \leftarrow y_{i} + \sum_{k=r_{i}}^{r_{i+1}-1} a_{k} x_{j_{k}}, \quad \text{for } i = 0, 1, \dots, M-1,$$

(1)

for an M-by-N matrix  $\mathbf{A} = (a_{i,j})_{i,j=0}^{M-1,N-1}$ , a source vector  $\mathbf{x} = (x_j)_{j=0}^{N-1}$  and a destination vector  $\mathbf{y} = (y_i)_{i=0}^{M-1}$ . The matrix  $\mathbf{A}$  is assumed to be given by K nonzero entries  $(i_k, j_k, a_k)_{k=0}^{K-1}$ , such that  $i_k$  and  $j_k$  are row and column offsets, respectively, of the nonzero matrix value  $a_k := a_{i_k,j_k}$ . Moreover,  $K \ll M \times N$  due to the matrix being sparse. It is also assumed that the nonzeros are sorted in ascending order of their row offsets,  $i_k$ . The row pointer  $r_i$  designates the position of the first nonzero of the ith row and  $r_{i+1} - 1$  points to the last nonzero of the ith row.

The kernel in Algorithm 1 consists of two nested loops, where the outer loop runs over the rows of the matrix and the inner loop iterates over the nonzeros of the current row. Two floating point operations, one multiplication and one addition, are performed for each matrix nonzero. While the matrix nonzero values (a) and column indices (colidx) are accessed in a streaming fashion, accesses to the source vector x are irregular and unpredictable. Finally, OpenMP is used to partition the rows of the matrix and distribute the work among threads in a shared memory parallel fashion.

#### 2.1.2 ORIGINAL ROOFLINE MODEL ANALYSIS

Algorithm 1 appears straightforward to analyse using the ORM (see also Vuduc et al.<sup>11</sup> for a similar analysis of an SpMV kernel that incorporates a register blocking optimisation). However,

<sup>&</sup>lt;sup>9</sup>Williams, Waterman, and Patterson, "Roofline: An Insightful Visual Performance Model for Multicore Architectures".

<sup>&</sup>lt;sup>10</sup>James D. Trotter, Johannes Langguth, and Xing Cai. "Cache simulation for irregular memory traffic on multi-core CPUs: Case study on performance models for sparse matrix–vector multiplication". *Journal of Parallel and Distributed Computing* 144 (2020), pp. 189–205. ISSN: 0743-7315. DOI: 10.1016/j.jpdc.2020.05.020.

<sup>&</sup>lt;sup>11</sup>Richard Vuduc et al. "Performance Optimizations and Bounds for Sparse Matrix-Vector Multiply". *Proceedings of the 2002 ACM/IEEE Conference on Supercomputing*. Baltimore, Maryland: IEEE Computer Society Press, 2002, pp. 1–35. DOI: 10.1109/SC.2002.10025.

```

1 void csrspmv(

2

int num_rows, int * rowptr, int * colidx,

double * a, double * x, double * y)

3

4 {

#pragma omp for

5

6

for (int i = 0; i < num_rows; i++) {</pre>

double z = 0.0;

7

for (int k = rowptr[i]; k < rowptr[i+1]; k++)</pre>

8

z += a[k] * x[colidx[k]];

9

y[i] += z;

10

11

}

12 }

```

**Algorithm 1:** Matrix-vector multiplication for a sparse matrix in compressed sparse row (CSR) storage format. OpenMP is used to partition the rows of the matrix and distribute the work among threads in a shared memory parallel fashion.

we will soon see that the irregular and data dependent accesses to the source vector x make matters more complicated, since they cannot be predicted ahead of time. On the surface, every iteration of the inner loop reads 20 bytes from memory (line 9), 4 bytes due to the column indices (colidx) and 8 bytes each due to the values of a and x, whereas every iteration of the outer loop writes 8 bytes to memory (line 10) for the destination vector y. For simplicity, we ignore writes to the destination vector, which anyway become negligible as long as the average number of nonzeros per row is large enough. Thus, concentrating on the inner loop, which performs two floating-point operations per iteration, the arithmetic intensity is  $\frac{1}{10}$  flop/B.

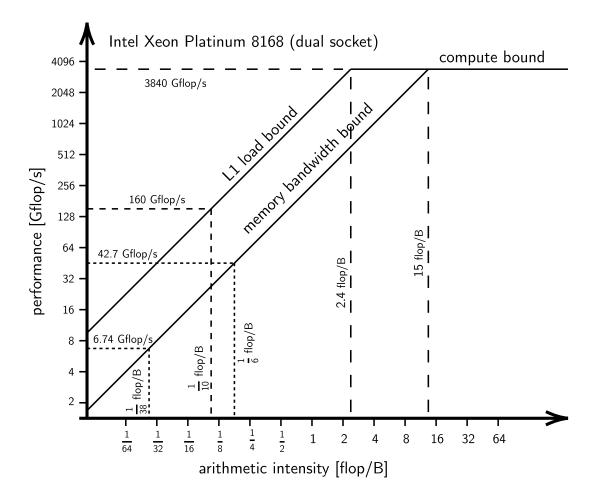

As an example, we consider a dual socket system with two Intel Xeon Platinum 8168 CPUs, each with 24 cores operating at 2.5 GHz, and a theoretical memory bandwidth of 256 GB/s. An ORM for this system is shown in Figure 2. In this example, the arithmetic intensity of Algorithm 1 implies an upper bound of 160 Gflop/s, assuming that the 20 bytes needed during each iteration of the inner loop are loaded in 1.5 cycles.<sup>12</sup> However, this is only possible with an already warm cache and a matrix with no more than about 2 700 nonzeros per CPU core (i.e., fewer than 130 000 nonzeros in total). Otherwise, the matrix cannot fit in the 32 KiB L1 cache of each core. Moreover, any matrix with more than about 5.8 million nonzeros will not even fit in the 66 MiB shared L3 cache and must therefore be read entirely from main memory. Although, since the L3 cache in the Skylake-X microarchitecture is non-inclusive,<sup>13</sup> it is arguably more appropriate to consider the 114 MiB combined size of the L2 and L3 caches instead, meaning that matrices with more than 10 million nonzeros will not fit.

In the case of cold caches or a sufficiently large matrix, 12 bytes must be read from main memory for each nonzero to obtain its value and column index. If we assume for now that the source vector resides entirely in cache,<sup>14</sup> the arithmetic intensity becomes  $\frac{1}{6}$  flop/B. With a theoretical memory bandwidth of 256 GB/s, the upper limit on performance becomes 42.7 Gflop/s.

<sup>&</sup>lt;sup>12</sup>The Skylake-X microarchitecture can serve two loads per cycle from the L1 cache.

<sup>&</sup>lt;sup>13</sup>Intel Corporation. Intel<sup>®</sup> 64 and IA-32 Architectures Optimization Reference Manual. 248966-040. Intel Corporation, 2018, Ch. 2.

<sup>&</sup>lt;sup>14</sup>Even in an ideal scenario, where the entire 1.5 MiB L1 cache is dedicated to storing the source vector, it will only fit in the cache for matrices with up to 196 608 columns. Similarly, the source vector cannot fit entirely in the L3 cache for matrices with more than 8.7 million columns. Within the combined size of the L2 and L3 caches, the source vector will not fit for matrices with more than 14.9 million columns.

**Figure 2** Original roofline model for sparse matrix-vector multiplication with the CSR storage format (see Algorithm 1) on a dual socket Intel Xeon Platinum 8168 (Skylake-X) multicore CPU system.

Note that this estimate is somewhat optimistic, since the actual memory bandwidth achieved in practice, as measured, for instance, by the STREAM benchmark,<sup>15</sup> is commonly found to be only about 70–80% of the theoretical maximum. A more conservative estimate would therefore be an upper performance limit of about 30 Gflop/s.

Now, even if the matrix is too large or the cache is cold, the source vector x may still benefit from reusing cached data. Whether or not the source vector values are reused in practice depends on details of the caching algorithm, as well as the irregular memory access pattern induced by the column indices of the matrix nonzeros and the order in which the nonzeros are arranged. The best case, as described above, yields an arithmetic intensity of  $\frac{1}{6}$  flop/B. But the worst case occurs when every access to the source vector must bring an entire cache line of 64 bytes from main memory, even though only a single 8-byte value is needed from the cache line in question. As a result, a total of 76 bytes must be read from main memory for every matrix nonzero. The arithmetic intensity is reduced to  $\frac{1}{38}$  flop/B, and the performance is limited to merely 6.74 Gflop/s, as shown in Figure 2.

The ratio between the best and worst case performance described above is  $\frac{38}{6} \approx 6.3$  times. In

<sup>&</sup>lt;sup>15</sup>John D. McCalpin. *STREAM: Sustainable Memory Bandwidth in High Performance Computers*. Department of Computer Science School of Engineering and Applied Science, University of Virginia. 2013. URL: https://www.cs.virginia.edu/stream/.

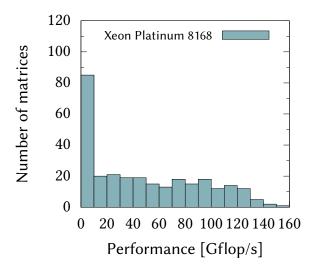

**Figure 3** *Performance of sparse matrix-vector multiplication with the CSR storage format (see Algorithm 1) for 289 real matrices from the SuiteSparse Matrix Collection with more than one million nonzeros on a dual socket Intel Xeon Platinum 8168 (Skylake-X) multicore CPU system.*

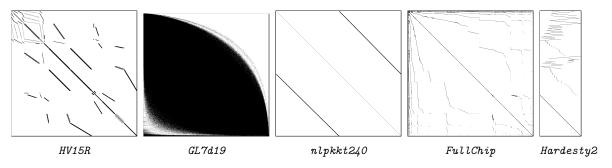

Figure 4 Sparsity patterns of a few sparse matrices from the SuiteSparse Matrix Collection.

reality, the performance of SpMV kernels, such as Algorithm 1, varies greatly depending on the matrix sparsity pattern (i.e., the location of the matrix nonzeros). This is illustrated by the spread in performance shown in Figure 3 for a selection of large, sparse matrices from the SuiteSparse Matrix Collection.<sup>16</sup> The performance is below 10 Gflop/s for almost a third of the matrices, but for the remaining matrices, the performance varies considerably, ranging all the way from 10 Gflop/s up to about 160 Gflop/s. To also demonstrate the diversity in the underlying sparsity patterns, Figure 4 shows the sparsity patterns of a few matrices that were used.

# 2.2 SPARSE CARM: IMPROVING ROOFLINE INSIGHTFULNESS FOR SPARSE COMPUTATIONS

Cache-Aware Roofline Model (CARM)<sup>17</sup> provides insightful indication of performance upperbounds of a micro-architecture with multiple levels in the memory hierarchy, which allows for visual application characterization, optimization and bottleneck detection. Similarly to other SoA roofline models, CARM is predominantly architecture-centric, i.e. it mostly considers architecture parameters (such as the maximum attainable memory bandwidth and peak compute throughput)

<sup>&</sup>lt;sup>16</sup>Timothy Davis and Yifan Hu. "The University of Florida Sparse Matrix Collection". ACM Transactions on Mathematical Software (TOMS) 38.1 (2011), pp. 1–25. ISSN: 1557-7295. DOI: 10.1145/2049662.2049663.

<sup>&</sup>lt;sup>17</sup>Ilic, Pratas, and Sousa, "Cache-aware Roofline model: Upgrading the loft".

when modeling the performance upper-bounds of a micro-architecture.

However, these performance maximums can only be attained by a small set of highly optimized and regular applications, or by carefully crafted assembly micro-benchmarks. In practice, the realistically attainable performance maximums do not only depend on the architecture capabilities, but also on the characteristics of the application (being executed on that architecture) and its ability to exploit those architecture maximums. For example, a naïve and non-vectorized SpMV kernel will never reached the maximum attainable performance that corresponds to the use of vector instructions.

To cope with these challenges and improve CARM insightfulness in these scenarios, we advocate herein a practical approach for CARM construction based on adCARM,<sup>18</sup> which specifically takes into account the application characteristics when determining the attainable maximums on a given architecture. The developed CARM-based model should also be able to adapt the characteristics of the input matrix, which can lead to an irregular memory access pattern, provoking performance degradation. This can cause even larger discrepancy between the application behavior and the modelled rooflines. Moreover, the kernel used for computations and the sparse matrix storage format must also be considered. With this aim, this work proposes a microbenchmarking methodology to construct CARM for SpMV kernels, by relying on synthetic dense matrices stored in sparse formats, in order to obtain the maximum attainable bandwidth of the systems when performing SpMV computations. By using dense matrices, the micro-benchmarks sequentially access all positions in the vector, which indeed maximizes the memory bandwidth of a system. Finally, while the presented evaluation focuses on the MKL Single-Precision SpMV kernel (mkl\_sparse\_s\_mv) and in the CSR format, the developed methodology can be extended to other kernels and formats.

Experimental results of this work were obtained in a Linux CentOS 7.5.1804 platform, with a eight-core Intel i7-7820X processor running at the fixed frequency of 3.60GHz, and 32GB of DRAM. All computation was performed using the Single-Precision sequential implementation of SpMV in the Intel® oneAPI Math Kernel Library<sup>19</sup> and hyper-threading and cache prefetching were disabled during testing.

### 2.2.1 ADAPTING CARM TO SPMV

The first step to achieve a CARM-based approach for SpMV kernels is to determine which matrix dimensions correspond to the maximum attainable bandwidth of the micro-architecture when performing MKL SpMV. As the L1 cache is the memory level that guarantees maximum transfer rate between the core and the memory hierarchy, this preliminary test evaluates the performance of the MKL SpMV kernel with different sizes of involved data structures, such that the input sparse matrix (A, stored in CSR format), input vector (X) and output vector (Y) always fit in L1 cache. This evaluation was performed with a single-thread, where the single precision SpMV computation was executed multiple times to guarantee a total of at least 250ms of kernel runtime.

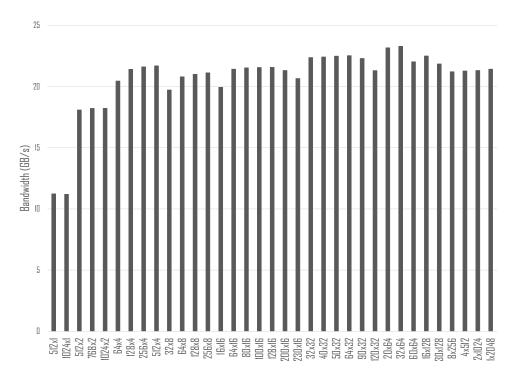

Preliminary bandwidth testing of several dense matrix dimensions, seen in Figure 5, shows that the matrices *20x64* and *32x64* as the dense parameters capable of delivering the highest performance when data structures involved in SpMV always fit in L1 cache. Considering the steady-state nature of these tests (i.e., SpMV kernel performed multiple times on warm caches), the streamed data structures in the SpMV kernel such as the CSR arrays (row pointer, column indices and non-zero values) and output Y vector, are only able to have reuse in a specific cache

<sup>&</sup>lt;sup>18</sup>Diogo Marques et al. "Application-driven Cache-Aware Roofline Model". *Future Generation Computer Systems* 107 (2020), pp. 257–273. ISSN: 0167-739X. DOI: https://doi.org/10.1016/j.future.2020.01.044. URL: https: //www.sciencedirect.com/science/article/pii/S0167739X19309586.

<sup>&</sup>lt;sup>19</sup>Intel Corporation. Intel® oneAPI Math Kernel Library. Intel. URL: https://software.intel.com/en-us/mkl.

Figure 5 Dense Preliminary Tests for Single Threaded MKL SpMV.

level if the total memory occupied does not exceed the capacity of that cache level, while the input X vector, for a small column size (of 64), maintains locality at L1 cache level.

However, in order to extend this testing methodology to the other cache levels, while keeping the reuse of X vector in L1 cache, the amount of rows in the dense matrix (A) is increased while maintaining 64 columns, expanding the memory occupied by the data structures. It is also possible to extend this methodology to evaluate the scenarios when the reuse of X vector occurs beyond the L1 cache, since the X vector locality depends on whether a specific cache level is able to fully store it. For these dense tests, the previous test can be repeated by selecting more columns for A matrix (which result in increasing the amount of elements in X vector), thus exceeding the cache capacity to store the X vector, in order to test the attainable bandwidths for other cache levels when the X vector locality is in the L2 and L3 cache or DRAM.

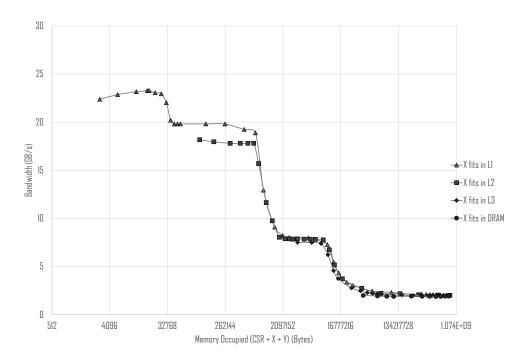

Applying this testing methodology to the entire memory hierarchy, under single-thread execution leads to the bandwidth curves presented in Figure 6. As it can be observed, when X vector fits inside L1 cache (dense matrix with 64 columns), the bandwidth reduces as the size of the remaining structures surpass the size of each memory level. For example, when all structures fit in L1 cache, a maximum bandwidth around 23.3GB/s is achieved, while 19.82GB/s is attained for L2 cache accesses, i.e., when all other data structures (except the X vector) surpass the L1 cache size. Moreover, when considering different sizes of X, L2 bandwidth reduction also occurs when X fits in L2 cache (8704 columns), instead of L1 cache. Between the two execution scenarios, the bandwidth drops from 19.8Gb/s (when X fits in L1) to 17.8GB/s (when X fits in L2), confirming that the higher bandwidth is obtained when X elements are reused from the memory level closer to the core. On the other hand, for L3 cache and DRAM, the attainable bandwidth is similar for all the different X vector sizes, since in these memory levels, the latency in accessing other data structures is high enough to not be affected by the locality of X.

This micro-benchmarking principle is also adopted for multi-threaded execution, where each

Figure 6 Bandwidth Curve for Single Threaded MKL SpMV.

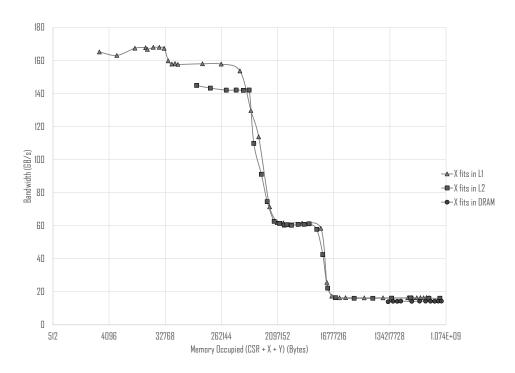

Figure 7 Bandwidth Curve for Multi Threaded MKL SpMV (8 cores).

thread shares the accesses to the sparse matrix A, while X and Y vectors are private to each thread. As it can be observed in Figure 7, the bandwidth in a multi-threaded (8 cores) environment shows similar behaviour as the single-threaded counterpart, with the memory bandwidth decreasing as

Figure 8 SpMV Adapted Cache Aware Roofline Model.

the accesses are served by memory levels further away from the core. As previously elaborated, the locality of X also affects the attainable L2 bandwidth, resulting in the bandwidth reduction of around 9% when X fits in L2 cache when compared to the scenario when X fits in L1 cache. Compared to the single-core tests, the bandwidth increases for all memory levels, achieving a maximum bandwidth of around 168, 158, 61.5, and 16.5 GB/s, for L1, L2, L3 and DRAM, respectively.

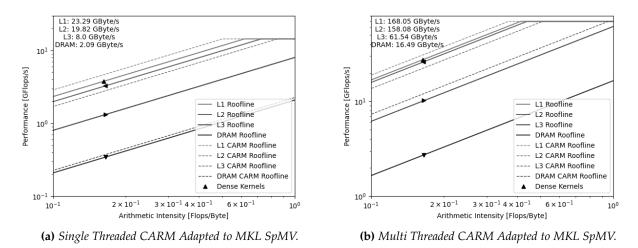

From the bandwidth values obtained in the tests presented in Figures 6 and 7, novel roofline models can be derived that better represent the performance upper-bounds of the SpMV kernel. The proposed roofline models are presented in Figures 8a and 8b, for single- and multi-threaded (8 cores) execution scenarios, respectively. Compared to the CARM roofs that correspond to scalar single-precision memory transfers (*i.e.*, the instructions used by MKL single-precision SpMV), the proposed rooflines have a lower L1 performance upper-bound given that the kernel is not only a streaming benchmark of the CSR and Y arrays but also contains the indirect access of the X vector, and these dependencies degrade the performance when access to the data is faster given the locality at the L1 cache level. When considering the proposed L2 rooflines, the performance is higher than the CARM roofs given that the locality of the X vector is preserved at the L1 while in the original roofs, streaming tests would have locality only in L2 cache. L3 and DRAM rooflines show little differences in performance.

# 2.2.2 IMPACT OF SPARSE MATRIX CHARACTERISTICS IN SPARSE CARM

Code in Listing 1 presents a naïve implementation of the SpMV computation kernel applied to a sparse matrix A represented in a CSR format, where vector *vals* contains the value of each row-major stored non-zero element, *cols* contains the column coordinate of each element, and *pointerB* and *pointerE* store the index of the first and last non-zero element in each row, respectively. Based on this implementation, the total number of loads and stores executed based on the characteristic of the matrix can be found in Table 1, and multiplying the sum of instructions by  $\beta_i$  (average number of bytes transfered per instruction), the total amount of bytes transferred to the core is obtained. Knowing that a SpMV kernel performs  $2 \times NNZ$  floating-point operations, with NNZ being the number of non-zero elements in the sparse matrix, the Arithmetic Intensity (AI) (as perceived by CARM) can be derived from equations 3 and 4.

| Memory Accesses |                   |                   |  |  |

|-----------------|-------------------|-------------------|--|--|

| Array           | Num LD            | Num ST            |  |  |

| у               | N <sub>rows</sub> | N <sub>rows</sub> |  |  |

| pointerB        | N <sub>rows</sub> |                   |  |  |

| pointerE        | N <sub>rows</sub> |                   |  |  |

| vals            | N <sub>nnz</sub>  |                   |  |  |

| cols            | N <sub>nnz</sub>  |                   |  |  |

| Х               | N <sub>nnz</sub>  |                   |  |  |

$$\mathrm{AI} = \frac{\mathrm{Floating\ Point\ Operations}}{\mathrm{Memory\ Accessed\ (bytes)}} \quad \text{(2)}$$

$$AI = \frac{2 \times N_{nnz}}{\beta_i \times (3 \times N_{nnz} + 4 \times N_{rows})} \quad (3)$$

$$\mathrm{AI} = \frac{2}{\beta_{\mathrm{i}} \times (3 + 4 \times \frac{N_{\mathrm{rows}}}{N_{\mathrm{nnz}}})} \tag{4}$$

| AI Limits                                        |                              |

|--------------------------------------------------|------------------------------|

| $Minimum AI(\frac{N_{nnz}}{N_{rows}} = 1)$       | $\frac{2}{\beta_i \times 7}$ |

| Maximum AI $(\frac{N_{nnz}}{N_{rows}} = \infty)$ | $\frac{2}{\beta_i \times 3}$ |

**Table 1** Arithmetic Intensity of Naive SpMV.

```

for(int i = 0 ; i < n_rows ; i ++){

y[i] = tmp;

for(int j = pointerB[i]; j < pointerE[i]; j++){

tmp += vals[j] * X[cols[j]];

}

y[i] = tmp;

}</pre>

```

### Listing 1: Naïve SpMV Kernel

From these equations, it is possible to conclude that differently from most applications, CARM AI of SpMV depends on the characteristics of the input matrix, in particular, the number of non-zeros per row (NNZ/N<sub>rows</sub>). In the case where there are no empty rows, the minimum AI corresponds to NNZ/N<sub>rows</sub> = 1, while maximum AI occurs when NNZ/N<sub>rows</sub>  $\rightarrow \infty$ . Moreover, since the performance in the memory region of the roofline models depends in the AI, the dependency between the AI and the characteristics of the input matrix indicates that different matrices have distinct performance upper-bounds.

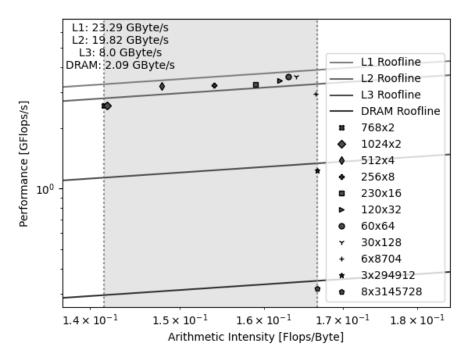

This range of AI can be experimentally verified by relying on dense synthetic matrices with different dimensions. Figure 9 presents this experimental evaluation, where highlighted in grey is the AI range attainable using the MKL SpMV in single precision ( $\beta_i = 4$ ). As it can be observed, the minimum AI corresponds to the dense matrices with 2 columns (AI  $\approx 0.14152$ ). As the number of non-zero elements per row increases, the AI shifts to the right, approaching and stabilizing at values close to the theoretical maximum, as it can be observed for matrices with more than 8704 columns (AI  $\approx 0.16666$ ).

#### 2.2.3 IMPROVING SPMV PERFORMANCE BY REORDERING

Given the memory access pattern of SpMV, the performance gains only occur if the accesses to vector X are improved, *e.g.*, X elements are reused in caches and/or accesses to X are coalesced. To achieve this, reordering techniques can be applied to the sparse matrix, in order to provide a more regular access pattern to X with improved data reuse. In order to evaluate the maximum performance gains that can be obtained with reordering, this work proposes a strategy that involves the creation of pairs of synthetic matrices. One of the matrices corresponds to the *worst*

Figure 9 AI Range Tests in MKL SpMV.

*case*, which aims at minimizing the reuse of X values as much as possible. On the other extreme, the second matrix mimics the *best case* execution scenario, where the locality on X is maximized. In each pair, the best case scenario must correspond to a specific permutation of rows and columns of the worst case scenario.

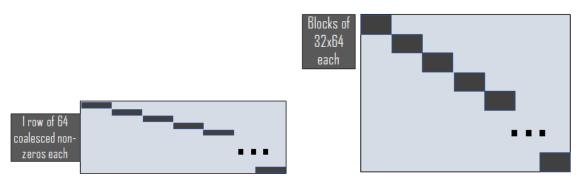

In order to maximize the reuse of elements in the X vector, the matrix for the *best case* scenario contains several dense blocks in the diagonal, each with  $p \times q$  elements. This organization aims at guaranteeing the maximum data locality and reuse of X at the level of each block. In particular, when processing a dense block, the q elements of X are fetched when processing the first row, and subsequently reused for each p row processed. To allow for maximum reuse, the value of q is selected such that the part of X accessed in each block fits in L1 cache, and it is a multiple of cache line size. With this structure for the best matrix, the worst case matrix must contains q non-zero elements per row, and p non-zero elements per column, in order to be transformed into the best case through row and column permutation.

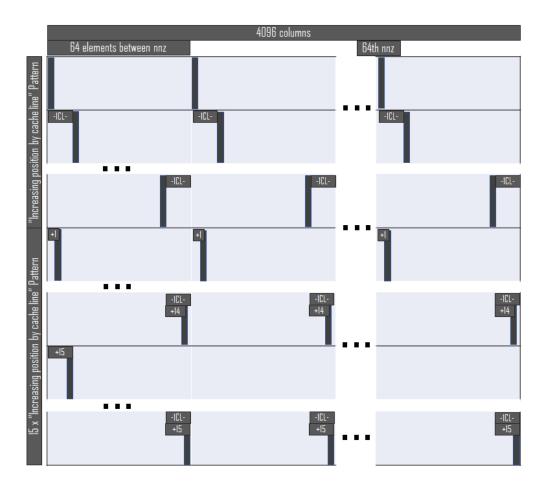

An example of the *worst case* matrix creation is presented in Figure 10, which considers blocks of a size  $1 \times 64$ . To avoid reuse of elements within a cache line, each of the 64 non-zero elements (in a single row) must be separated by at least a cache line size (e.g., 16 elements in single precision). This fact requires choosing a column size that allows for the even distribution of the elements (e.g., 4096 columns allows that each non-zero element is separated by 4096/64 = 64 positions). To also avoid cache line re-utilization between rows when accessing X vector, each non-zero element of the next row is shifted by one cache line to the right. This is repeated until all the cache-lines are exhausted, i.e., the maximum amount of cache lines that can be allocated between two consecutive elements in a single row. For example, when considering 4096 columns and 64 positions between each non-zero in a single row, a total of 4 rows are needed to repeat this pattern (since 64 positions correspond to 4 cache lines, i.e. 64/16 = 4). This distribution can

**Figure 10** Worst Matrix Example for 1x64 blocks

be observed in Figure 10 within the first block of 4 rows described as "*Increasing position by cache line* Pattern".

This pattern for block of rows is repeated for the next group of  $4 \times 64$  non-zero elements, where the position of each non-zero corresponds to the one from the previous block of rows, but incremented by one position. This distribution can be observed in Figure 10 being repeated for the next 15 blocks of rows described as "15 x *Increasing position by cache line* Pattern". Each of the blocks of 4 rows increase the position of each non-zero element by one until all elements of the X vector are accessed by the *worst case* matrix. This allows for the reordering of this non-zero distribution into a pattern as shown in Figure 11a. Having this distribution being repeated 32 times enables the reordering into the best case matrix with the diagonal of 32x64 blocks (see Figure 11b).

Using this strategy, for a specific dense block dimension of the best case matrix (i.e.,  $p \times q$ ), the only other parameter to choose is the amount of columns, which should preferably be divisible by the column size of the blocks for even distribution in the worst case matrix. The NNZ and row size of the matrix depends on the amount of blocks that fit in the best case matrix diagonal with the chosen block dimensions and column size.

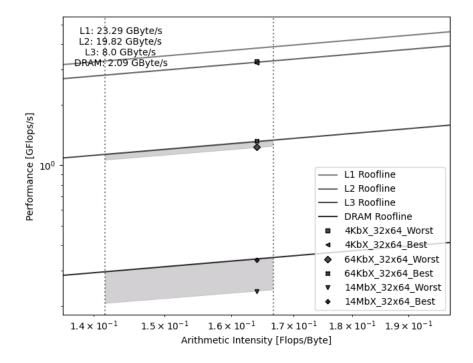

Figure 12 presents the evaluation of several best and worst case matrices in the Sparse CARM, for single threaded workloads with single precision data. Since according to the preliminary testing presented in Figure 5 the maximum bandwidth is achieved for a block size of  $32 \times 64$ , this

(a) Resulting Best Matrix with 1x64 blocks

**(b)** Best Matrix if Worst Matrix for 1x64 blocks repeats pattern 32 times.

**Figure 12** ST-Best case and Worst case Matrices for 32x64 blocks

experimental evaluation is performed with p = 32 and q = 64 (Figure 11b).

As it can be observed in Figure 12, the groups of matrices that fit in DRAM (14MbX) and L3 (64KbX) memory levels reveal that significant performance improvements can be achieved between the worst and the best cases. However, the group fitting in L2 cache (4KbX), which also are the smallest matrices that are able to be created for a block of  $32 \times 64$  using this strategy, show little to no performance improvement. This effect occurs due to data re-utilization between the rows that have the non-zero elements only one column apart from each other, reducing the gap in cache reuse between the worse and best case matrices.

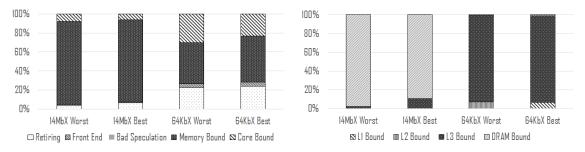

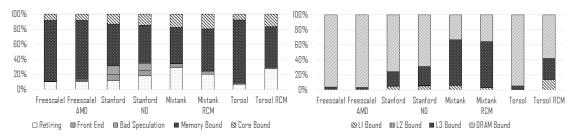

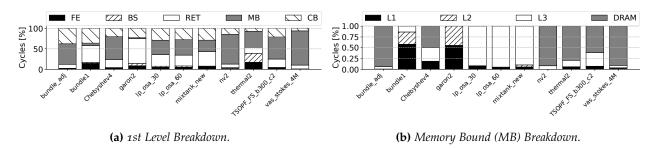

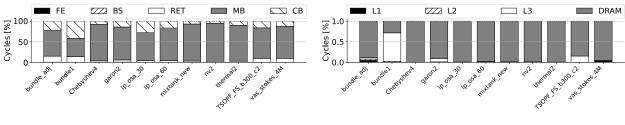

To further verify the obtained results, the Intel VTune Top-Down breakdown is presented in Figure 13. When analyzing the first level of the Intel VTune Top-Down results presented in Figure

(a) Top Down VTune Analysis of ST Best Worst Matrices (b) Memory Bound VTune Analysis of ST Best Worst Matrices

Figure 13 VTune Analysis of Synthetic Worst/Best Matrices in single-thread.

**Figure 14** MT-Best case and Worst case Matrices for 32x64 blocks

13a, it is possible to verify that there is an increase in the retiring component from the worst case scenario to the best case matrix. Moreover, the memory bound breakdown of Top-Down (Figure 13b) shows an increase of the L3 Bound component for the 14MbX best case matrix, and the appearance of the L1 Bound component for the 64KbX matrix. Thus, it is possible to conclude that the performance improvement achieved by reordering the worst matrices arises from better cache utilization, due to a more regular access pattern.

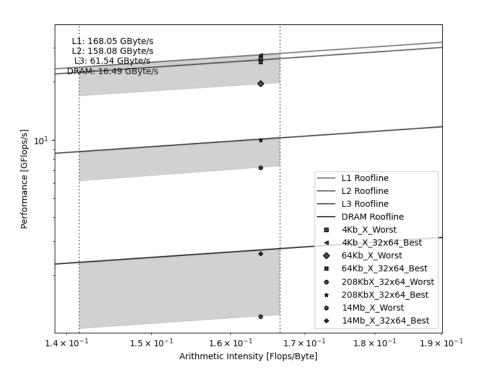

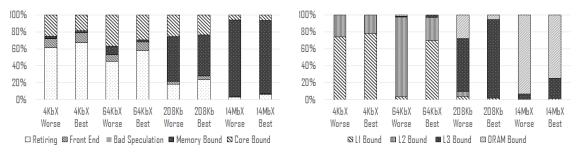

This strategy is also applied to a multi-threaded (8 cores) scenario, by performing static row partitioning of the input sparse matrix among threads, with shared access to X and Y vector. As it can be observed in Figure 14, similar to the single-thread test, there is a clear improvement in the SpMV performance when reordering the worst case matrix, especially for L3 cache (208KbX) and

(a) Top Down VTune Analysis of MT Best Worst Matrices (b) Memory Bound VTune Analysis of MT Best Worst Matrices

Figure 15 VTune Analysis of Synthetic Worst/Best Matrices in multi-thread.

DRAM (14MbX). For example, from worst case to the best case, a maximum speedup of around 2.10x for DRAM matrices, and 1.39x for L3 matrices can be expected. With this row partitioning, each thread will only transfer 1/8th of the matrix, which will change the locality of some of the matrix groups. This effect can be observed for the 64KbX matrices, which were located below the L3 bandwidth roof for the single-threaded tests, while in the multi-threaded tests they are positioned below the L2 roofline, thus indicating a maximum speedup of 1.28x for matrices that have locality in this cache level.

The increase in the performance is once more due to better locality and regularity in the memory accesses to vector X. As observed in the first level of Top-down analysis (see Figure 15a), there is an increase in the retiring component for all tested matrices when moving from the worst case to the best case execution scenarios, indicating that after reordering the core is being more utilized. In the memory bound breakdown (Figure 15b), it is also possible to observe the effects of reordering in the accesses to the memory hierarchy. In the case of the 4KbX and 64KbX matrices (that aim at exercising the reordering upper-bounds for L1 and L2 caches, respectively), there is an increase in the L1 bound component after reordering, thus leading to increased performance. In the case of the larger matrices, *i.e.*, 208KbX and 14MbX, the contribution of the L3 bound increases greatly after the reordering, while the DRAM bound component reduces. In all four test cases, both Top-Down and Sparse CARM show that reordering the input matrix can provide significant speedups by just improving the accesses to vector X, leading to higher utilization of components closer to the core.

In order to represent the possible speedups for matrices with locality focused on each specific cache-level, the ranges of performance gain obtained with the best and worse case matrices for both single and multi-threaded scenarios are highlighted in grey in Figures 12 and 14, respectively.

Given that the previous evaluation with synthetic matrices has shown the potential to achieve significant speedups in SpMV by reordering the input sparse matrix, this work also provides an evaluation of the MKL SpMV performance when using real matrices reordered with state-of-theart algorithms, for single and multi-threaded execution. The considered reordering algorithms are Reverse Cuthill-McKee (RCM),<sup>20</sup> Approximate Minimum Degree (AMD),<sup>21</sup> Nested Dissection (ND),<sup>22</sup> a partial implementation of GrayRO,<sup>23</sup> and on two matrices, the reordering algorithms

<sup>&</sup>lt;sup>20</sup>E. Cuthill and J. McKee. "Reducing the Bandwidth of Sparse Symmetric Matrices". Association for Computing Machinery, 1969.

<sup>&</sup>lt;sup>21</sup>Patrick R. Amestoy, Timothy A. Davis, and Iain S. Duff. "An Approximate Minimum Degree Ordering Algorithm". *SIAM Journal on Matrix Analysis and Applications* 17.4 (1996), pp. 886–905.

<sup>&</sup>lt;sup>22</sup>Alan George. "Nested Dissection of a Regular Finite Element Mesh". *SIAM Journal on Numerical Analysis* 10.2 (1973), pp. 345–363.

<sup>&</sup>lt;sup>23</sup>Haoran Zhao et al. "Exploring Better Speculation and Data Locality in Sparse Matrix-Vector Multiplication on

| Matrix Name | Rows    | Cols    | NNZ      | Size (KBytes)    |

|-------------|---------|---------|----------|------------------|

| Freescale1  | 3428755 | 3428755 | 17052626 | ≈ 173400         |

| patents     | 3774768 | 3774768 | 14970767 | ≈ 161190         |

| torso1      | 116158  | 116158  | 8516500  | $\approx 67900$  |

| Stanford    | 281903  | 281903  | 2312497  | $\approx$ 21370  |

| ns3Da       | 20414   | 20414   | 1679599  | ≈ 13360          |

| poisson3Db  | 85623   | 85623   | 2374949  | ≈ 19560          |

| sme3Db      | 29067   | 29067   | 2081063  | ≈ 16600          |

| mixtank_new | 29957   | 29957   | 1990919  | ≈ 15900          |

| SS          | 1652780 | 1652780 | 34753577 | ≈ <b>2</b> 90880 |

| Fullchip    | 2987012 | 2987012 | 26621983 | ≈ 242990         |

| wb-edu      | 9845725 | 9845725 | 57156537 | $\approx 561920$ |

**Table 2**Real matrices retrieved from SuiteSparse.

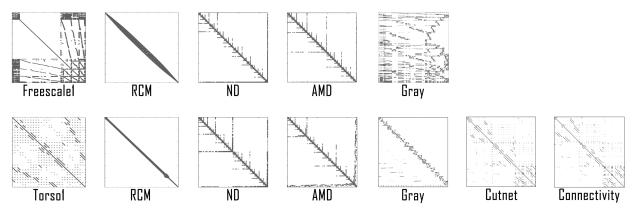

Figure 16 Reordering Algorithms applied to Matrices

included in the Patoh partition library:<sup>24</sup> cutnet and connectivity. A set of eleven matrices from SuiteSparse are considered for evaluation, as presented in Table 2. This set of matrices are real, general and non-complex, and have a diverse number of rows, columns and non-zero elements, covering a wide range of execution scenarios. Examples of how different reordering algorithms affect the disposition of the non-zero elements can be seen in Figure 16, *e.g.* in the matrices where RCM was used, it can be seen how the non-zero elements are more distributed along the diagonal and this reduction in the spread of the elements may provide performance benefits due to more coalesced accesses to the X vector.

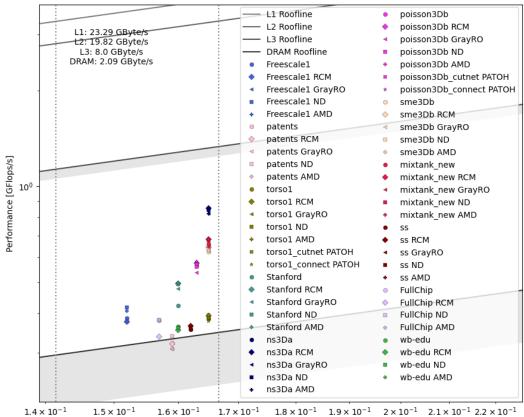

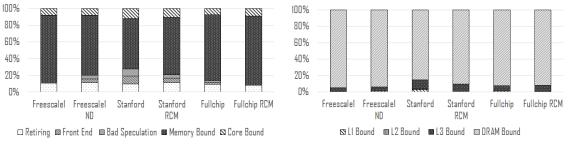

Figure 17 presents the characterization of the matrices with different reordering algorithms in the sparse CARM for single-threaded execution. As it can be observed, the considered reordering methods do not guarantee performance improvements for all matrices. In fact, several reordered matrices suffer from performance reduction (*e.g.* Fullchip RCM and Freescale RCM), while other have small gains in performance. For example, Fullchip attained a speedup of 1.08x with ND, while RCM provided 1.17x speedup for Stanford. Further insights can be obtained through the Intel VTune Top-Down. As it can be observed with the Top-Down method for Freescale1, Stanford and FullChip (Figure 18), Freescale1 reordering with ND and Standford reordered with RCM

Intel Xeon". 2020 IEEE 38th International Conference on Computer Design (ICCD). 2020.

<sup>&</sup>lt;sup>24</sup>Ümit V Çatalyürek and Cevdet Aykanat. "Patoh (partitioning tool for hypergraphs)". *Encyclopedia of parallel computing*. Springer, 2011, pp. 1479–1487.

Arithmetic Intensity [Flops/Byte]

Figure 17 ST Real and Reordered Matrices

(a) Top Down VTune Analysis of ST Real Matrices

(b) Memory Bound VTune Analysis of ST Real Matrices

Figure 18 VTune Analysis of some real and reordered matrices in single-thread.

have an increase in the retiring contribution, and a reduction in the memory bound component. This indicates that the bottlenecks after reordering are slightly more related to the core, which explains their performance increase of 8% for Freescale1 and 17% for Stanford. On the other hand, FullChip with RCM has a reduction in the retiring component together with an increase in the memory bound and core bound, which leads to a performance decrease of 11%.

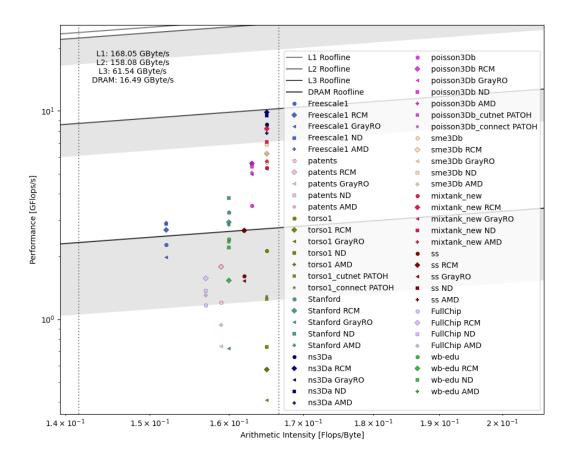

Figure 19 MT Real and Reordered Matrices

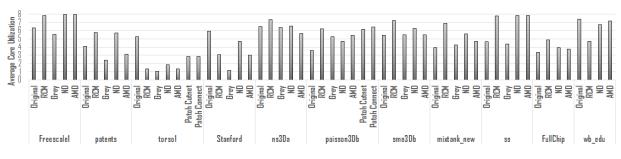

The same matrices and reordering algorithms were also tested in multi-threaded fashion for 8 threads total, with each thread being assigned a partition based on equal distribution of the rows with shared access to the X and Y vector. The representation of these matrices in the multi-threaded SpMV adapted CARM (see Figure 19) show a similar trend to the singlethread experiments, since the reordering algorithms can either provide speedups or slowdowns depending on the matrix. Moreover, in multi-thread execution is also necessary to take into account the impact of load balancing in the performance of the application. Since the experiments proposed in this work focused on an even partition of the rows between threads, the number of non-zero elements performance by each thread may differ, resulting in data imbalance, degrading performance. By observing the average core utilization of each matrix, presented in Figure 21, it is possible to observe that reordering algorithms may result in an increase of the load balancing (all 8 cores are being utilized), while in other in may provoke serious imbalance issues. For example, matrix Poisson3Db has an increase of the average core utilization from 3.6 to 6.2 when using RCM. On the other hand, Torso1 has a reduction from 5.3 to 1.35 in the core utilization when using RCM. This explains their characterization in the Sparse CARM, since Poisson3Db has a speedup of 1.6x and torso1 a slowdown of 0.27x.

All these effects can also be observed in the Top-Down method, presented in Figure 20.

(a) Top Down VTune Analysis of MT Real Matrices (b) Memory Bound VTune Analysis of MT Real Matrices

Figure 20 VTune Analysis of some real and reordered matrices in multi-thread.

For example, applying AMD to Freescale1, results in performance gain, although no noticeable changes occur in the Top-Down metrics. Thus, the speedup in this matrix is mainly due to the improved load balancing attained after reordering, as the average core utilization increases from 6.31 to 7.95. In contrast, reordering Stanford with ND algorithm improves the locality of the accesses to X vector, indicated by the increasing in the retiring and L3 bound components. Despite ND causing load imbalance (average core utilization drops from 5.92 to 4.7), the performance of this matrix still improves after reordering. For Mixtank\_new matrix, applying RCM deteriorates locality of accesses to X vector, as can be seen by the increase of the memory bound component and L1 bound indication, which still results in a performance gain, due to improvement of load balancing from 3.92 to 6.87. Analysing the effect of RCM applied to torso1, locality of X is greatly improved as the memory bound component lowers significantly while retiring increases, and observing the changes in memory bound analysis, the DRAM bound indication reduces with increased L1 and L3 components. Despite this, as previously mentioned, torso1 reduces the core utilization to 1.35 when applied RCM reordering algorithm, resulting in slowdown due to inferior resource utilization.

Highlighted in grey in Figures 17 and 19 are the performance improvement intervals expected when reordering is applied, which are obtained from the synthetic worse and best case matrices by considering different matrix sizes that guarantee locality at a specific cache level. As it can be observed in Figure 17, the majority of the real matrices in the single-threaded scenario are positioned above the DRAM roof and below the performance improvement interval for the L3 cache, which indicates that tested matrices are only partially exploiting locality in L3 cache, while still being limited by the DRAM accesses. In the multi-threaded scenario (see Figure 19), some matrices are positioned within the performance intervals for both L3 cache and DRAM. However, one can also observe that some matrices are placed below the highlighted performance improvement interval, *e.g.* RCM, ND and Gray reordering of torso1 matrix are positioned below the DRAM interval. Besides the potential poor data reuse, in these cases, the sparse CARM characterization also suggests the load balancing issues, which prevents the computation performed on the reordered matrix to exploit the performance limits corresponding to the 8 cores execution.

Observing analysed results on reordering as a performance improvement method for SpMV, synthetic best and worst case matrices are able to represent possible performance gains depending on the memory locality. While multi-threaded testing exhibits higher performance gains compared to single-threaded, when utilizing real matrices to tests these margins, load balancing proves to be an impediment in correlating improved locality through reordering and performance optimization, as the former can also affect how balanced the workload is split among working threads. Future work on this subject will focus on ways to represent load balancing in CARM for multi-threaded tests as well as the usage of partitioning techniques combined with reordering

Figure 21 Average Core Utilization for Multi-threaded testing

algorithms for a more clear analysis on how performance is impacted by changes in cache locality without load balancing being a factor.

# 2.3 MANSARD ROOFLINE MODEL: SPARSE KERNELS ANALYSIS

When modeling the performance upper-bounds, SoA roofline models<sup>25</sup> may oversimplify the back-end of the micro-architectures by just focusing on a subset of functional units and the maximum attainable bandwidth of different memory hierarchy levels. As such, those models do not consider other hardware components that may limit the performance in any Out-of-Order (OoO) processor, especially the ones related to the retirement of instructions, such as, number of Retirement Slots (RS), Reorder Buffer (ROB) and Physical Register File (PRF). Instead, these models evaluate the performance upper-bounds by only considering the isolated performance limits of the different hardware resources, thus giving the illusion of infinite retirement and OoO windows. Moreover, when concurrently executing non-memory and memory instructions, the limited capacities of ROB and PRF can constraint the number of in-flight memory requests, preventing applications from achieving maximum memory bandwidth and increasing the impact of memory latency, especially when accessing the "slower" memory levels. This can hinder the ability of roofline models to provide accurate characterization of applications that suffer from latency issues. This is the case of several sparse kernels, that due to their irregular memory patterns are highly likely to have bottlenecks related to the latency of Last Level Cache (LLC) and DRAM.

# 2.3.1 MANSARD ROOFLINE MODEL

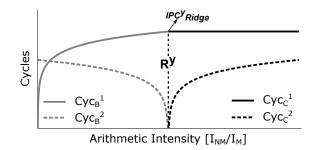

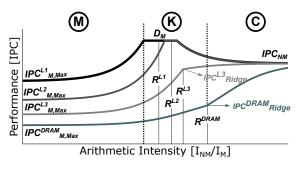

To address the main drawbacks of the SoA roofline models, the Mansard Roofline Model  $(MaRM)^{26}$  considers all the instructions retired by an application, representing performance as Instructions Retired per Cycle (IPC). Since MaRM uses the instruction domain instead of the operations domain, its AI differs from standard roofline models. In MaRM, the AI is defined as the number of non-memory instructions ( $I_{NM}$ ) over the number of memory instructions ( $I_M$ ). Thus, the ridge point of memory level 'y' ( $R^y$ ), *i.e.*, the point where memory transfers and computations are completely overlapped in time, is represented as the performance of the non-memory instructions ( $IPC_{NM}$ ) over the maximum sustainable bandwidth of memory level 'y' ( $IPC_{M,Max}^y$ ), where  $y \in \{L1, L2, ..., LLC, DRAM\}$ .

For representing performance as IPC, it is indispensable to incorporate the retirement limits

<sup>&</sup>lt;sup>25</sup>Williams, Waterman, and Patterson, "Roofline: An Insightful Visual Performance Model for Multicore Architectures"; Ilic, Pratas, and Sousa, "Cache-aware Roofline model: Upgrading the loft".

<sup>&</sup>lt;sup>26</sup>Diogo Marques, Aleksandar Ilic, and Leonel Sousa. "Mansard Roofline Model: Reinforcing the Accuracy of the Roofs". *ACM Trans. Model. Perform. Eval. Comput. Syst.* 6.2 (2021). ISSN: 2376-3639. DOI: 10.1145/3475866. URL: https://doi.org/10.1145/3475866.

| (A) AI = R <sup>y</sup> | (B) Al < R <sup>y</sup> | (C) AI > R <sup>y</sup>  |

|-------------------------|-------------------------|--------------------------|

| MEM                     | MEM                     | МЕМ                      |

| MEM                     | MEM                     | МЕМ                      |

| ()                      | ()                      | () ХМ                    |

| Non MEM                 | Non MEM +               | Non MEM ∓                |

| Non MEM ™               | Non MEM                 | Non MEM _≊               |

| ()                      | ()                      | ()                       |

| MEM                     | MEM                     | Non MEM                  |

| MEM                     | MEM                     | Non MEM &                |

| ()                      | MEM                     | Non MEM ¥                |

| Non MEM<br>Non MEM      | MEM<br>MEM<br>()        | Non MEM<br>Non MEM<br>() |

Figure 22 Execution scenarios for different application types.

of OoO Central Processing Units (CPUs). Due to the limited number of retirement slots, microarchitectures can only retire a limited number of instructions per cycle. Hence, the maximum attainable performance ( $P_{\alpha}^{y}(AI)$ ) is limited by the maximum dispatch rate ( $D_{M}$ ) of the microarchitecture such that

$$\mathsf{P}^{\mathsf{y}}_{\mathsf{a}}(\mathsf{A}\mathsf{I}) \leqslant \mathsf{D}_{\mathsf{M}},\tag{5}$$

where  $D_M$  was 4 instructions per cycle in previous Intel micro-architectures, and 5 instructions per cycle in the newest Sunny Cove core architecture.

To include the impact of the ROB in MaRM, the three execution scenarios in Figure 22 are considered. These execution scenarios are representative of applications or application kernels with different AIs (expressed in  $\frac{I_{NM}}{I_M}$ ), which according to roofline approaches are able to attain the maximum performance in different regions of the models. Scenario **A** fully overlaps memory and non-memory instructions, *i.e.*, AI = R<sup>y</sup>; in Scenario **B**, applications are memory bound (AI < R<sup>y</sup>); and Scenario **C** portrays workloads in the compute bound region (AI > R<sup>y</sup>).

At the ridge point (scenario A), the ROB has several blocks containing  $B_M$  memory instructions and  $B_{NM} = B_M \times R^y$  non-memory instructions. For example, an application with an average of 2 loads per store has  $B_M = 3$  and  $B_{NM} = 3R^y$ . Since the amount of in-flight memory requests (IF<sub>M</sub>) corresponds to the total number of memory instructions in the ROB, IF<sub>M</sub> can be calculated as

$$IF_{M} = B_{M} \times \left[ \frac{ROB_{eff}}{B_{M} + B_{NM}} \right] = B_{M} \times \left[ \frac{ROB_{eff}}{B_{M} \times (R^{y} + 1)} \right], \tag{6}$$

where ROB<sub>eff</sub> is the effective ROB size.

When accessing high latency memory levels, the blocks  $B_M + B_{NM}$  that fit in the ROB can only start retiring after the first memory request is completed. Thus, the execution time of the blocks  $B_M + B_{NM}$  contained in the ROB is approximately the latency of the corresponding memory level 'y' (Lat<sup>y</sup>(IF<sub>M</sub>)), thus the performance of the micro-architecture at the ridge point (IPC<sup>y</sup><sub>R</sub>(IF<sub>M</sub>)) is given by

$$IPC_{R}^{y}(IF_{M}) \approx \frac{IF_{M} \times (R^{y} + 1)}{Lat^{y}(IF_{M})} =$$

$$= (R^{y} + 1) \times IPC_{M}^{y}(IF_{M}),$$

(7)

where  $IPC_{M}^{y}(IF_{M})$  is the effective memory bandwidth of the level 'y' restricted by the number of in-flight requests. This parameter is related to  $Lat^{y}(IF_{M})$  through Little's Law  $(IPC_{M}^{y}(IF_{M}) \times$

**Figure 23** Illustration of cycles of the proposed MaRM.

$Lat^{y}(IF_{M}) = IF_{M}).^{27}$

Memory bound (scenario B) and compute-bound (scenario C) applications also aim at overlapping non-memory and memory instructions, but since their AI is different from R<sup>y</sup> they consist of two components each. The first one overlaps memory and non-memory instructions in the same fashion as scenario A. The second component only contains instructions of a single type. Since in scenario B, the AI is lower than R<sup>y</sup>, there are more memory instructions than non-memory instructions. Thus, the first component contains all non-memory instructions overlapped with  $\frac{I_{NM}}{R^y}$  memory transfers, corresponding to a total of  $I_{NM} + \frac{I_{NM}}{R^y}$  instructions, while the second component is organized as in scenario A, it is executed at the rate of IPC<sup>y</sup><sub>R</sub>(IF<sub>M</sub>). In the second component, instructions are retired at the maximum sustainable memory bandwidth (IPC<sup>y</sup><sub>M,Max</sub>), since there are enough requests in the ROB to attain the maximum bandwidth. Hence, the number of cycles necessary to execute a memory-bound application (Cyc<sub>B</sub>) is given by:

$$Cyc_{B}^{y}(AI, IF_{M}) = \frac{I_{NM} + \frac{I_{NM}}{R^{y}}}{IPC_{R}^{y}(IF_{M})} + \frac{I_{M} - \frac{I_{NM}}{R^{y}}}{IPC_{M,Max}^{y}} = \frac{AI \times I_{M}(1 + \frac{1}{R^{y}})}{IPC_{R}^{y}(IF_{M})} + \frac{I_{M} \times (1 - \frac{AI}{R^{y}})}{IPC_{M,Max}^{y}}.$$

(8)

On the other hand, the first code portion of compute-bound applications (scenario C) contains all memory instructions overlapped with  $I_M \times R^y$  non-memory instructions, *i.e.*, a total of  $I_M + I_M \times R^y$  instructions, retired at the speed of  $IPC_R^y(IF_M)$ . The second component contains  $I_{NM} - I_M \times R^y$  non-memory instructions retiring at the performance of the non-memory instructions (IPC<sub>NM</sub>). Thus, the number of cycles necessary to execute the application C (Cyc<sub>C</sub>) can be calculated as:

$$Cyc_{C}^{y}(AI, IF_{M}) = \frac{I_{M} + I_{M} \times R^{y}}{IPC_{R}^{y}(IF_{M})} + \frac{I_{NM} - I_{M} \times R^{y}}{IPC_{NM}} =$$

$$= \frac{R^{y} \times I_{M}(1 + \frac{1}{R^{y}})}{IPC_{R}^{y}(IF_{M})} + \frac{I_{M} \times (\frac{AI}{R^{y}} - 1)}{IPC_{M,Max}^{y}}.$$

(9)

Equations 8 and 9 are illustrated in Figure 23, each represented by their respective components, *i.e.*,  $Cyc_B^1$  and  $Cyc_B^2$  from  $Cyc_B^y(AI, IF_M)$ , and  $Cyc_C^1$  and  $Cyc_C^2$  from  $Cyc_C^y(AI, IF_M)$ . There is a relation between the components of both equations. Regarding the first components,  $Cyc_C^1$  is always constant and equal to  $Cyc_B^1$  at the ridge point, while the second components of the equations have the same absolute value, *i.e.*,  $|Cyc_B^2| = |Cyc_C^2|$ . Thus, from the analysis of Figure 23,

<sup>&</sup>lt;sup>27</sup>John DC Little. "A proof for the queuing formula: L= λ W". Operations research 9.3 (1961), pp. 383–387.

Figure 24 Illustration of MaRM.

Equations 8 and 9 can be unified in a single equation such that the application execution time  $(Cyc_{App})$  is given by:

$$Cyc_{App} = I_{M} \times \left( \frac{\min(AI, R^{y})(1 + \frac{1}{R^{y}})}{IPC_{R}^{y}(IF_{M})} + \frac{|\frac{AI}{R^{y}} - 1|}{IPC_{M, Max}^{y}} \right).$$

(10)

Finally, from Equations 5 and 10, it is possible to derive the MaRM performance (IPC $_a^y(AI, IF_M)$ ):

$$IPC_{a}^{y}(AI, IF_{M}) = \min\left(\frac{I_{M} + I_{NM}}{Cyc_{App}}, D_{M}\right).$$

(11)

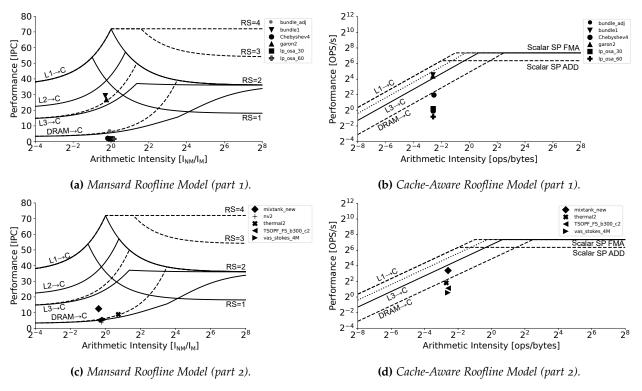

Figure 24 illustrates the proposed MaRM. As it can be observed, MaRM includes in the memory-bound region the entire memory hierarchy, with each level represented by their maximum sustainable bandwidth. The compute-bound region of the model is limited by the performance of the non-memory instructions. In contrast to SoA roofline models, the roofs in MaRM have a format similar to a "hill", and the memory roofs are no longer diagonal lines. Since MaRM performance cannot surpass the maximum retirement rate of the micro-architecture, flat regions may occur in the model, indicating areas where the application is limited by the number of retirement slots. This is observed for the L1 roof in Figure 24. While in CARM the ridge point corresponds to the minimum AI that allows attaining maximum performance for any memory levels, in MaRM this does not occur for L<sub>3</sub> and Dynamic Random Access Memory (DRAM). Due to the high latency of these memory levels, their effective bandwidth depends on the amount of concurrent memory requests. Thus, the ridge points of the L<sub>3</sub> cache and DRAM do not correspond to the point where maximum performance is achieved when accessing those memory levels. In fact, the performance continues to increase beyond the ridge point due to the growing contribution of the compute instructions, asymptotically approaching to the maximum performance of the compute units. On the other hand, for L1 and L2 caches, the micro-architecture is able to attain the maximum sustainable bandwidth for the entire range of AI, until reaching the ridge point. Hence, the ridge point in MaRM inherits the properties of CARM for L1 and L2 caches.

As it can be observed in Figure 24, MaRM contains three main regions: memory region, where application performance is limited by the memory bandwidth of each memory level; compute region, delimited by the maximum retirement rate of the system; and mixed region (K), where the bottlenecks can be either related to the memory accesses or the maximum achievable performance. The bottleneck identification is performed by plotting a vertical line at the application AI. The intersections right above and below the application dot correspond to the main sources of inefficiencies. Depending on the region where the application is located, a set of optimizations can

Figure 25 Benchmarking results for Mansard Roofline Model.

be derived to improve the execution time. In the memory region, the optimization should focus on improving the memory accesses, while in the compute region vectorization methods can be employed to improve application execution. In the mixed region, techniques from both memory and compute regions might be used according to the bottlenecks identified at each optimization phase.

In the mixed region of the roofs correspondent to the "slower" memory levels, applications are expected to be limited by both memory bandwidth and latency. Compared to the SoA roofline models, this property is exclusive to MaRM, and arises from the ROB impact to the bandwidth of the memory subsystem and retirement of instructions. This effect becomes more relevant as the AI approaches the ridge point. Moreover, since MaRM represents performance as IPC, the model is oblivious to the vector width. For this reason, certain optimizations lead to lower execution time with reduced IPC. For example, in current Intel micro-architectures, an application heavily dominated by scalar Integer (INT) instructions may be closer to the retirement roof of 4RS. However, by vectorizing the INT instructions, the IPC of the application will tend to the roofs correspondent to the retirement rate of SIMD ALU (3RS in most recent Intel CPUs).

Another scenario is the optimization of a compute-bound application dominated by Scalar instructions. This workload will be limited by the horizontal roof corresponding to the performance of these instructions (for example, 2RS for Floating-Point (FP) scalar instructions), indicating that there is no room for optimization, although the application can be easily sped-up by using vector instructions. Thus, when a scalar application is already on top of the computational roof that resembles the maximum throughput that its instruction mix can achieve, the recommendation is to attempt the code vectorization.

While the drop in IPC might look counter intuitive, it increases MaRM intuition regarding the ability to evaluate the vectorization efficiency. For example, when the throughput of scalar ad vector instructions is equal (*e.g.*, FP AVX512), three scenarios can occur after vectorization: **1)** IPC remains constant, indicating that the vectorization attained maximum efficiency and the execution time reduced proportionally to the vector size; **2)** the IPC reduced, hinting that the contribution of memory accesses and/or vectorization overheads increased and the vectorization did not attain 100% efficiency; and **3)** the IPC is equal to 1/vector\_width, corresponding to the worst case scenario where the vectorization did not resulted in any benefit and the execution time remains almost the same.

MaRM depends on the relation between the effective ROB size with the number of in-flight requests and the attainable memory bandwidth. This relation can be obtained through microbenchmarking. Regarding the effective ROB size, the micro-benchmark is constructed such that a

| Matrix           | #NNZ        | #Rows     | #Columns  |

|------------------|-------------|-----------|-----------|

| Bundle_adj       | 20,207,907  | 513,351   | 513,351   |

| bundle1          | 770,811     | 10,581    | 10,581    |

| Chebyshev4       | 5,377,761   | 68,121    | 68,121    |

| garon2           | 373,235     | 13,535    | 13,535    |

| Lp_osa_30        | 604,488     | 4,350     | 104,374   |

| Lp_osa_60        | 1,408,073   | 10,280    | 243,246   |

| mixtank_new      | 1,990,919   | 29,957    | 29,957    |

| thermal2         | 8,580,313   | 1,228,045 | 1,228,045 |

| nv2              | 37,475,646  | 1,453,908 | 1,453,908 |

| TSOPF_FS_b300_c2 | 8,767,466   | 56,814    | 56,814    |

| vas_stokes_4M    | 131,577,616 | 4,382,246 | 4,382,246 |

**Table 3**SuiteSparse matrices used for the evaluation.

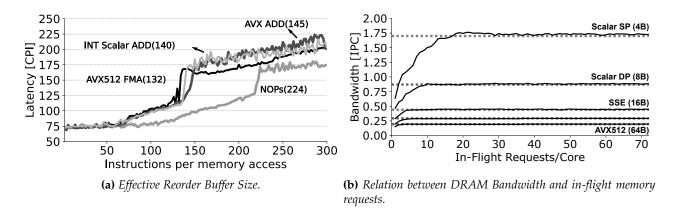

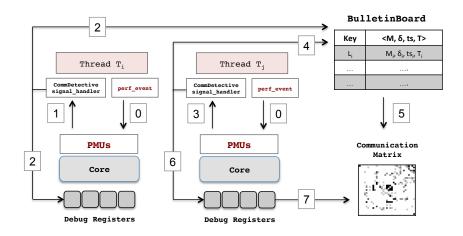

significant increase in the execution time occurs at the ROB limit. The experimental evaluations of the effective ROB size for No-Operation (NOP), 512-bit-AVX (AVX512) Fused Multipy-Add (FMA) instructions, Advanced Vector Extension (AVX) Additions (ADD) instructions and scalar integer additions (INT ADD) are presented in Figure 25a. Since NOPs do not use any register during execution, the latency drastically increases approximately at the size of the ROB, *i.e.*, 224 entries. For AVX512 FMA instructions, the memory latency increases when there are 132 instructions per memory access, *i.e.*, around 78.6% of the vector PRF capacity (168 entries), while for AVX ADD instructions, the effective ROB size is close to 145 entries. This non-ideal behavior indicates the existence of additional bottlenecks in different components of the core pipeline. The results also show that the effective ROB size depends on the instructions. Similar scenario occurs for the INT ADD test, with an effective ROB size around 140 entries.