# Complete performance and energy models

| Deliverable No:<br>Deliverable Title:<br>Deliverable Publish Date: | D1.4<br>Complete performance and energy models<br>31 March 2023          |

|--------------------------------------------------------------------|--------------------------------------------------------------------------|

| Project Title:                                                     | SPARCITY: An Optimization and Co-design Framework for Sparse Computation |

| Call ID:                                                           | H2020-JTI-EuroHPC-2019-1                                                 |

| Project No:                                                        | 956213                                                                   |

| Project Duration:                                                  | 36 months                                                                |

| Project Start Date:                                                | 1 April 2021                                                             |

| Contact:                                                           | sparcity-project-group@ku.edu.tr                                         |

## List of partners:

| Participant no. | Participant organisation name                       | Short name | Country  |

|-----------------|-----------------------------------------------------|------------|----------|

| 1 (Coordinator) | Koç University                                      | KU         | Turkey   |

| 2               | Sabancı University                                  | SU         | Turkey   |

| 3               | Simula Research Laboratory AS                       | Simula     | Norway   |

| 4               | Instituto de Engenharia de Sistemas e Computadores, | INESC-ID   | Portugal |

|                 | Investigação e Desenvolvimento em Lisboa            |            |          |

| 5               | Ludwig-Maximilians-Universität München              | LMU        | Germany  |

| 6               | Graphcore AS                                        | Graphcore  | Norway   |

## CONTENTS

- 1 Introduction 1

- 1.1 Objectives of This Deliverable 1

- 1.2 Work Performed 2

- 1.3 Deviations and Counter Measures 3

- 1.4 Resources 3

- 2 Cache-aware roofline modeling for efficient sparse computing and hardware co-design 3

- 2.1 Sparse CARM: Improving roofline insightfulness for sparse computations 3

- 2.1.1 Sparse-aware CARM for Performance 4

- 2.1.2 Analysis and Usability of Sparse-Aware CARM 5

- 2.1.3 Sparse CARM Analysis: Reordering Algorithms and Load Balancing 6

- 2.1.4 Energy Efficiency Analysis and Optimization 12

- 2.2 Roofline-based Hardware Scaling for Efficient Sparse Computing 16

- 2.2.1 SpMV Implementation 16

- 2.2.2 Architecture and Methodology 16

- 2.2.3 Exploring Cache Dynamics 16

- 2.2.4 Exploring the range of arithmetic intensities 18

- 2.2.5 Improving SpMV Efficiency with Roofline-based Architecture Scaling 19

- 2.2.6 Conclusion 22

- 3 Exploring the processing limits of SpMM and TTM on CPU/GPU systems 23

- 3.1 Analysis of sparse matrix multiplication on a GPU device 23

- 3.1.1 Targeted Device, Reported Metrics and Execution Variables 23

- 3.1.2 GEMM on CUDA Cores and on Tensor Cores 25

- 3.1.3 SpMM on CUDA cores 27

- 3.1.4 SpMM on Tensor Cores 30

- 3.1.5 SpMM on Sparse Tensor Cores 33

- 3.1.6 Comparison between the evaluated SpMM approaches 36

- 3.2 Identifying the Tensor-Times-Matrix Upper-bounds on CPU and GPU devices 38

- 3.2.1 Data-parallel Tensor-Times-Matrix (TTM) Processing 40

- 3.2.2 CPU/GPU TTM performance upper-bounds with synthetic sparse tensors 43

- 4 Communication and Profiling tools for Emerging Microarchitectures 55

- 4.1 Extending Communication Analysis Tools to AMD Multicores 55

- 4.1.1 IBS Driver 56

- 4.1.2 Interaction Between IBS Driver and Profiling Tools 57

- 4.1.3 Evaluation: COMDETECTIVE on AMD vs Intel 59

- 4.1.4 Evaluation: REUSETRACKER on AMD vs Intel 60

- 4.1.5 Conclusion 60

- 4.2 Investigating Cache Partitioning for SpMV on the A64FX Processor 60

- 4.2.1 Using Fujitsu's C Compiler for Cache Partitioning in SpMV on A64FX 61

- 4.2.2 Experimental Setup 61

- 4.2.3 Performance Results 61

- 4.2.4 Cache Partitioning Profiling Tool 62

- 5 Digital SuperTwin 64

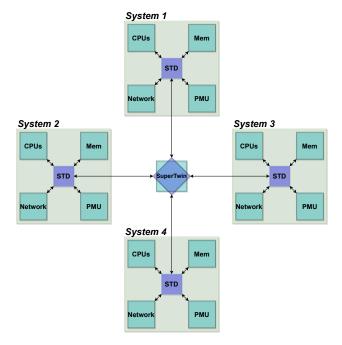

- 5.1 SuperTwin Description 64

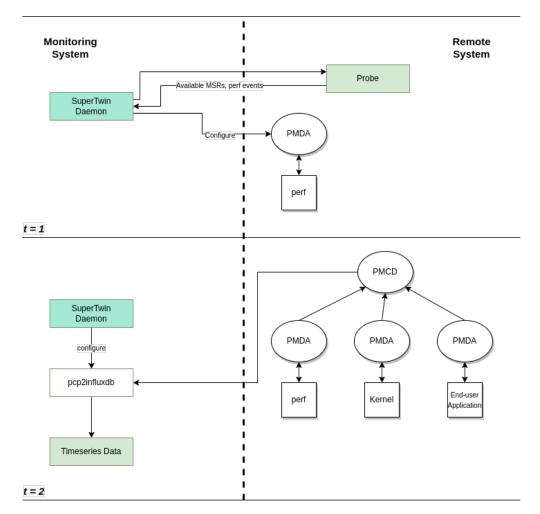

- 5.2 Sampling Framework 69

- 5.3 Monitoring 70

- 5.4 Observation 71

- 5.5 Generation of Dashboards 74

- 5.6 Benchmarks 74

- 5.7 Evaluation of SuperTwin Readings via Performance Co-Pilot 77

- 5.7.1 Resource Use of Sampling 78

- 5.7.2 Throughput and Integrity of Reported Metrics 79

- 5.7.3 Accuracy of Hardware Performance Counter Sampling 85

- 5.7.4 Overhead of Measurements 88

- 5.8 Summary of activities 88

## 6 Conclusions 90

7 History of Changes 94

## 1 INTRODUCTION

The SPARCITY project is funded by EuroHPC JU (the European High Performance Computing Joint Undertaking) under the 2019 call of Extreme Scale Computing and Data Driven Technologies for research and innovation actions. SPARCITY aims to create a supercomputing framework that will provide efficient algorithms and coherent tools specifically designed for maximizing the performance and energy efficiency of sparse computations on emerging High Performance Computing (HPC) systems, while also opening up new usage areas for sparse computations in data analytics and deep learning.

Sparse computations are commonly found at the heart of many important applications, but at the same time it is challenging to achieve high performance when performing the sparse computations. SPARCITY delivers a coherent collection of innovative algorithms and tools for enabling both high efficiency of sparse computations on emerging hardware platforms. More specifically, the objectives of the project are:

- to develop a comprehensive application and data characterization mechanism for sparse computation based on the state-of-the-art analytical and machine-learning-based performance and energy models,

- to develop advanced node-level static and dynamic code optimizations designed for massive and heterogeneous parallel architectures with complex memory hierarchy for sparse computation,

- to devise topology-aware partitioning algorithms and communication optimizations to boost the efficiency of system-level parallelism,

- to create digital SuperTwins of supercomputers to evaluate and simulate what-if hardware scenarios,

- to demonstrate the effectiveness and usability of the SPARCITY framework by enhancing the computing scale and energy efficiency of challenging real-life applications.

- to deliver a robust, well-supported and documented SPARCITY framework into the hands of computational scientists, data analysts, and deep learning end-users from industry and academia.

## 1.1 OBJECTIVES OF THIS DELIVERABLE

The objective of this deliverable is to document sparse-aware performance, power and energyefficiency models for devices with emerging architectures. Through the identification of the potential for performance and energy-efficiency of different sparse computation workloads, the purpose of these models is to detect compute and memory bottlenecks and suggest optimizations. These optimizations can include modifications to the kernel performing sparse computations that is under study, suggesting specific core and memory frequencies through exploiting Dynamic Voltage and Frequency Scaling (DVFS), and/or in regard to hardware design decisions that can be taken to improve execution given a metric of interest. Another objective is to develop profiling tools for identifying and analysing data movement. Tools capable of performing inter-process/inter-thread communication profiling, reuse distance analysis and cache partitioning/mapping are of utmost importance to achieve efficient mapping of the different types of sparse computations to emerging hardware architectures and devices. Finally, advances in the development of Digital SuperTwin targeting supercomputing platforms, which can seamlessly

SparCity

integrate the proposed models and tools, enable a high-throughput and precise collection of data and more insightful modeling, which paired with advanced visualization capabilities results in a more straightforward identification of how to take action.

## **1.2 WORK PERFORMED**

In this deliverable, we provide an extensive study focused on the strengths and usability of the proposed extensions to the Cache-Aware Roofline Model (CARM) for efficient sparse computing (sparse CARM), for which a new construction methodology and a novel micro-benchmarking strategy have been proposed as part of Deliverables 1.2 and 4.2 of the SPARCITY project. In addition, in this deliverable, we include in-depth explanations on the complete model interpretation methodology and usability of the proposed model, and we report the outcomes of its evaluation in the context of the use of matrix reordering techniques applied on synthetic and real-world sparse matrices. We also provide a novel roofline-based evaluation strategy that aims at assessing the variation in performance, power consumption and energy efficiency for a range of sparse kernels' Arithmetic Intensity (AI)s when scaling the operating frequency of the CPU cores. Furthermore, a performance analysis of an SpMV hand-tuned assembly implementation has been performed on a RISC-V microarchitecture. Also relying on CARM, the range of arithmetic intensities of the used algorithm has been thoroughly examined taking into account the cache dynamics of the targeted microprocessor. The compiled knowledge and modeling techniques can be used to identify the demands of sparse computations on current platforms with RISC-V processors and/or to guide the design of novel more capable and domain-specific processors for efficient sparse computations.

Sparse Matrix-Matrix Multiplication (SpMM) methods relying on different sparse formats, and considering different sparsity levels, have been profiled using different combinations of core and memory frequencies on a state-of-the-art GPU across both traditional CUDA cores and AI-oriented tensor cores. The different SpMM alternatives have been cross-compared, using as a baseline a state-of-the-art General Matrix Multiplication (GEMM) implementation, which has also been tuned with DVFS. Several applications rely on contractions between tensors of other orders, such as Tensor Times Matrix (TTM), which represents a contraction between a multi-dimensional tensor of arbitrary order and a second-order tensor. We derived approaches tackling sparse TTM and examined their performance bounds at processing both real and synthetic inputs on CPU and GPU microarchitectures. In addition, this deliverable compiles insights resulting from the exploration for sparse matrix operations of DVFS, a key mechanism of today's computing devices to enable achieving high levels of performance and energy-efficiency.

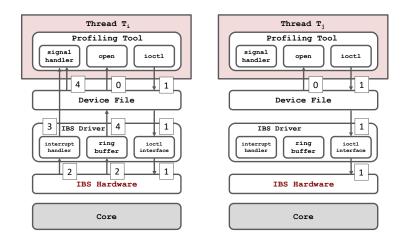

We extended the profiling tools elaborated in Deliverable 1.2 to target AMD x86 microarchitectures. Low-overhead inter-thread communication (COMDETECTIVE) and reuse distance (REUSETRACKER) analysis is achieved using the instruction-based sampling (IBS) facility and debug registers present in AMD processors. These tools have relevant features not available in other profiling tools, such as the capability of taking into account true and false sharing and measuring reuse distance in private and shared caches at a low overhead. Those features have been implemented through modification of a Linux kernel module that allows interfacing with the IBS hardware. The tools have been experimentally evaluated on a set of representative benchmarks, achieving high accuracy at a lower overhead than cycle accurate simulators and code instrumentation tools. Furthermore, we analyzed the impact of the cache partitioning methods proposed in Deliverable 1.2 in the context of SpMV execution targeting the A64FX processor, which has an embedded cache partitioning mechanism named sector cache. Partitioning and mapping program objects to specific cache partitions is performed at runtime through the use of compiler directives. Experimental evaluation demonstrated that using the sector cache allowed in most cases to improve execution in regard to performance and memory bandwidth utilization when processing matrices from cardiac electrophysiology. Relying on dynamic binary instrumentation, we developed a profiling tool that predicts the number of cache misses, with and without the use of the sector cache, from reuse distance histograms. The predictions produced by the profiling tool integrating the proposed cache partitioning methods have been demonstrated to closely match real measurements.

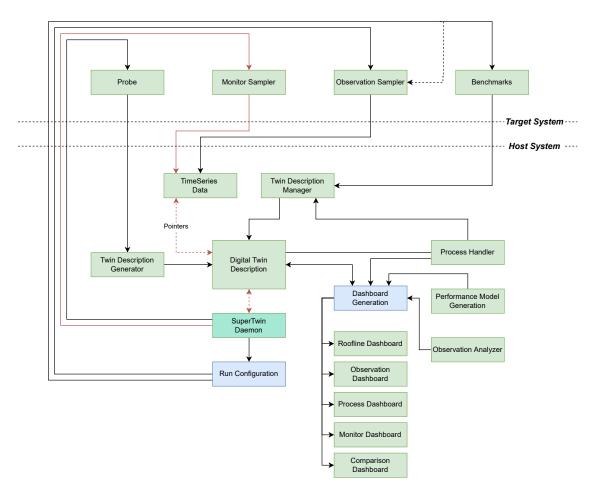

The initial stages of designing a prototype of SuperTwin, a digital replication framework, had been presented in Deliverable 1.2. In this deliverable, we document new developments for this framework, to which several novel and advanced features have been added. The current version of SuperTwin has additional augmentation and semantical query abilities, as-well new benchmarking capabilities, automatic generation of dashboards with support for real-time and per-request monitoring, and CARM modeling with integrated visualization. SuperTwin has been evaluated in regard to the throughput and integrity, as part of a study performed on four different systems under different sampling frequencies and with a varying amount of reported events.

## **1.3 DEVIATIONS AND COUNTER MEASURES**

There was no deviation from the work plan.

## 1.4 **RESOURCES**

As also envisioned in the project proposal, the herein elaborated modeling approaches had undergone further improvements and developments over the initial ones reported in the previous deliverables. As such, it is expected that further extensions of the proposed models and tools will be reported in subsequent deliverables, as well as maintained and regularly updated on the respective SPARCITY Github repositories.

# 2 CACHE-AWARE ROOFLINE MODELING FOR EFFICIENT SPARSE COMPUTING AND HARDWARE CO-DESIGN

## 2.1 SPARSE CARM: IMPROVING ROOFLINE INSIGHTFULNESS FOR SPARSE COMPUTATIONS

In order to enable accurate measurement of performance and power consumption upper-bounds of the micro-architecture when performing sparse computations, we proposed a novel microbenchmarking strategy in Deliverable 4.2 of the SPARCITY project. In Deliverable 1.2, we also proposed a new methodology for sparse-aware CARM construction, which relies on the proposed micro-benchmarking strategy and is capable of more accurately characterizing sparse computation kernels and their ability to utilize the micro-architecture computation resources. The sparseaware CARM is also able to provide more precise insights regarding the bottlenecks of sparse computations, as well as, to identify the best optimization steps that should be considered to improve their performance. In this deliverable, we provide an extensive study that demonstrates the insightfulness and usability of the sparse-aware CARM, while we also reveal the complete construction and interpretation methodology behind the proposed model. Furthermore, an in-depth validation and characterization is performed using a set of synthetic and real-world sparse matrices from standard matrix collections (*e.g.* Suite Sparse<sup>1</sup>) in both single- and multithreaded execution scenarios. For this evaluation, we also apply several of the most commonly used reordering techniques for sparse matrices: Reverse Cuthill-McKee (RCM), Approximate Minimum Degree (AMD), Nested Dissection (ND), GrayRO based on Zhao et.al.'s work<sup>2</sup> and two algorithms from the Patoh library.<sup>3</sup> By using the proposed model to visualise the changes in cache locality, we aim at verifying the ability of these reordering schemes to better utilize the computational power available in the micro-architecture, as well as their potential to provide performance improvements. A characterization methodology is also proposed in order to tackle load balancing issues that may arise in multi-threaded execution scenarios, which allows for further improvements in the model's insightfulness. Finally, a novel roofline-based evaluation methodology is adopted in order to assess the variation in performance, power consumption and energy efficiency for a range of kernel's Als when scaling the operating frequency of the CPU cores.

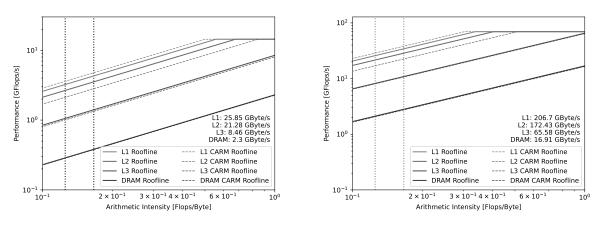

#### 2.1.1 SPARSE-AWARE CARM FOR PERFORMANCE

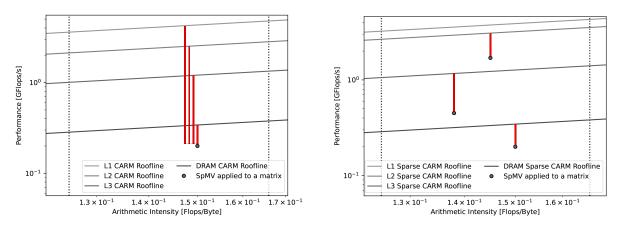

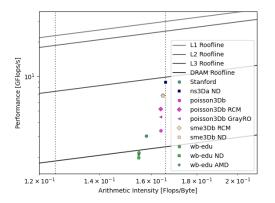

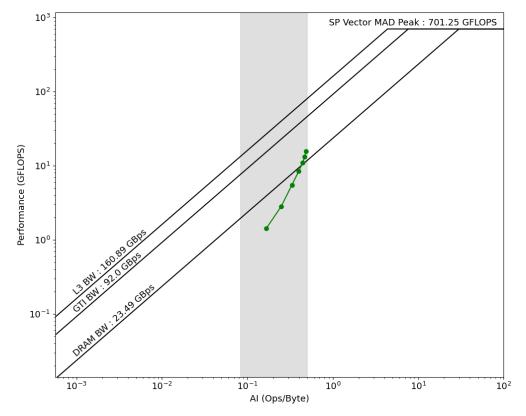

To validate the proposed sparse-aware CARM, we conducted an extensive experimental campaign on a Linux CentOS 7.5.1804 platform, with an eight-core Intel i7-7820X processor running at the fixed frequency of 3.60GHz with 32KB of L1 Data cache, 1MB of L2 cache, 11MB of L3 cache and 32GB of DRAM running at 2133MHz, with prefetching and hyper-threading deactivated. The proposed sparse-aware CARMs for this execution platform are presented in Figures 1 and 2, which are obtained for Sparse Matrix Vector Multiplication (SpMV) computation where the vector elements fit in the L1 cache and for single- and multi-threaded (8 cores) execution scenarios, respectively. For this evaluation, an open-source SpMV kernel, in x86 assembly, was specifically developed (as documented in Deliverable 4.2), which attains performance close to the corresponding Intel MKL kernel, while facilitating the algorithm analysis.

Figure 2 Multi-Threaded SP Sparse CARM

As it can be observed in Figures 1 and 2, compared to the dashed original CARM roofs achieved with scalar and single-precision instructions, used in the tested x86 assembly SpMV

<sup>&</sup>lt;sup>1</sup>Timothy A Davis and Yifan Hu. "The University of Florida sparse matrix collection". ACM Transactions on Mathematical Software (TOMS) 38.1 (2011), pp. 1–25.

<sup>&</sup>lt;sup>2</sup>Haoran Zhao et al. "Exploring Better Speculation and Data Locality in Sparse Matrix-Vector Multiplication on Intel Xeon". 2020 IEEE 38th International Conference on Computer Design (ICCD). IEEE. 2020, pp. 601–609.

<sup>&</sup>lt;sup>3</sup>Ümit V Çatalyürek and Cevdet Aykanat. "Patoh (partitioning tool for hypergraphs)". *Encyclopedia of parallel computing*. Springer, 2011, pp. 1479–1487.

Figure 3 AI Variation according to NNZ per row in Single Threaded Execution.

kernel, the proposed sparse-aware CARM achieves a lower L1 performance. This reduction in the maximum attainable performance for the L1 cache is mainly due to indirect accesses to the vector elements and memory accesses to multiple arrays. The dependencies between all those transfers lead to performance degradation when data is being retrieved from the L1 cache. When considering the proposed L2 rooflines, the performance is higher than the CARM roofs given that the locality of the vector elements is preserved at the L1 cache (while in the original roofs, streaming tests would have locality only in L2 cache). L3 roofline is slightly higher than the CARM, however the diminished difference in performance entails that the higher latency in accessing the vector elements continually stored in the L1 cache, due to the dependencies related to indirectly accessing the former. New DRAM rooflines also show little differences in performance, further justifying this performance impact.

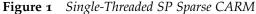

The vertically dotted lines shown in Figures 1 and 2 represent the theoretical AI range of the x86 Assembly SpMV kernel (see Deliverable 4.2). This range can be experimentally verified by relying on dense synthetic matrices with different dimensions. Figure 3 presents this experimental evaluation, where highlighted in grey is the AI range attainable using the x86 assembly SpMV kernel in single precision ( $\beta_i = 4$ ). As it can be observed, the minimum AI corresponds to the dense matrices with 1 column (AI = 0.125). As the number of non-zero elements per row increases, the AI shifts to the right, approaching and stabilizing at values close to the theoretical maximum, as it can be observed for matrices with more than 8704 columns (AI  $\approx$  0.16666).

### 2.1.2 ANALYSIS AND USABILITY OF SPARSE-AWARE CARM

The CARM derives its insight on attainable performance from the representation of the applications relative to the rooflines of the model, thus facilitating the optimization process. However, the sparse-aware CARM and corresponding rooflines are created based on different principles, given that sparse computation and corresponding performance not only depends on the utilized kernel but also on the sparse matrix to compute upon, thus providing different insights from the original model. As the attained rooflines are not only architecture-based but also related to the used kernel, *i.e.* using bandwidth values retrieved from micro-benchmarking (as documented in Deliverable 4.2), the adapted model is now a representation of how the computation upon a specific sparse matrix is able to utilize the performance capabilities of the micro-architecture, bound by the characteristics and inefficiencies of the sparse algorithm utilized. There is also another difference concerning the attainable performance and its association with the warm-cache nature of the performed testing. The rooflines were built from micro-benchmarking bandwidth values obtained using dense matrices stored in Compressed Sparse Row (CSR) for warm-cache SpMV computation, where all involved data structures are stored in the respective memory level, while the vector elements fit in the L1 cache. Given that all accesses to matrix data are performed in a sequential and cohesive manner and that total data involved in the computation is always the same, the optimization path is restricted to matrix reordering, where row and column permutation vectors are applied to the matrix in order to optimize the accesses to the vector. This means that, for a warm-cache scenario, a sparse matrix, whose SpMV involved data structures only fit inside a specific cache level, cannot exceed the performance of the corresponding memory roofline, as optimization through reordering only affects the accesses to the vector elements.

(a) CARM representation of a SpMV kernel applied to a sparse (b) Sparse CARM representation of different matrices computed matrix and perceived attainable performance.

Figure 4 Comparison between the two CARM representations in a sparse computation scenario.

Figure 4 graphically represents the attainable performance portrayed by the original CARM approach and the sparse-aware CARM approach. An example of a SpMV kernel computing upon a matrix is presented as grey dots in both models, and the red lines represent the attainable performance through optimization, where the original model portrays an misleading representation of the application. This is due not only to the rooflines not being built considering limitations of the sparse computation, but also the represented attainable performance by applying recommended optimization strategies for memory bound kernels is unlikely to maximize the applications' use of the computational power of the micro-architecture. Comparatively, profilling using the Sparse CARM portrays a realistic scenario regarding maximum performance in each memory level, with the kernel limitations properly considered, and attainable performance is limited by the memory level where the total size of the involved data structures are located.

## 2.1.3 SPARSE CARM ANALYSIS: REORDERING ALGORITHMS AND LOAD BALANCING

Given that the results presented in Deliverable 1.2 have shown the potential to achieve performance gains with Intel MKL SpMV by reordering the input sparse matrices, we extend herein this performance evaluation by considering the x86 assembly SpMV code. For this purpose, we focus on using real sparse matrices, representing them in the Sparse CARM, and applying state-of-the-art reordering algorithms, in single and multi-threaded execution. The considered reordering algorithms are RCM,<sup>4</sup> AMD,<sup>5</sup> ND,<sup>6</sup> the reordering algorithms included in the *Patoh* partition library:<sup>7</sup> cutnet and connectivity applied to two matrices, and a reordering algorithm created based on the work proposed by Zhao et. al,<sup>8</sup> named GrayRO. A set of eleven matrices from Suite Sparse<sup>9</sup> are considered for evaluation, as presented in Table 1. This set of matrices are real, general and non-complex, and have a diverse number of rows, columns and non-zero elements, covering a wide range of execution scenarios.

| Matrix Name | Rows    | Cols    | NNZ      | Size (KBytes)    |

|-------------|---------|---------|----------|------------------|

| Freescale1  | 3428755 | 3428755 | 17052626 | ≈ 173400         |

| patents     | 3774768 | 3774768 | 14970767 | $\approx$ 161190 |

| torso1      | 116158  | 116158  | 8516500  | $\approx 67900$  |

| Stanford    | 281903  | 281903  | 2312497  | $\approx$ 21370  |

| ns3Da       | 20414   | 20414   | 1679599  | ≈ 13360          |

| poisson3Db  | 85623   | 85623   | 2374949  | $\approx$ 19560  |

| sme3Db      | 29067   | 29067   | 2081063  | ≈ 16600          |

| mixtank_new | 29957   | 29957   | 1990919  | $\approx$ 15900  |

| SS          | 1652780 | 1652780 | 34753577 | $\approx$ 290880 |

| Fullchip    | 2987012 | 2987012 | 26621983 | ≈ 242990         |

| wb-edu      | 9845725 | 9845725 | 57156537 | $\approx$ 561920 |

**Table 1**Real matrices retrieved from SuiteSparse.

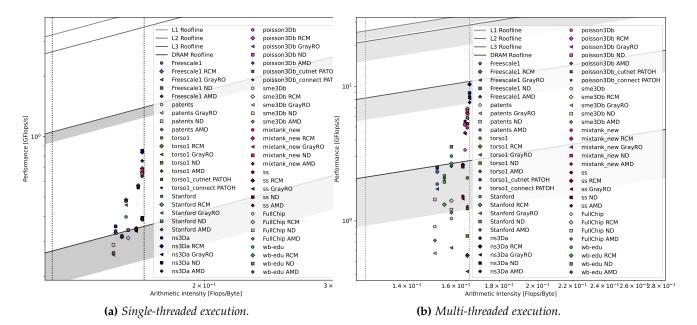

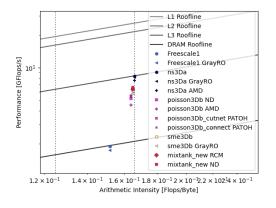

Figure 5a presents the characterization of the matrices with different reordering algorithms in the Sparse CARM for single-threaded execution. As it can be observed, the considered reordering methods do not guarantee performance improvements for all matrices. In fact, several reordered matrices suffer from performance reduction (*e.g.* Fullchip RCM and Freescale RCM), while other have small gains in performance. For example, Freescale1 attained a speedup of 1.05x with ND, while RCM provided 1.21x speedup for Stanford.

When taking into consideration the insight provided by the proposed modelling approach, the maximum performance (in warm-cache conditions) that the SpMV kernel can achieve when computing upon a specific sparse matrix is the roofline located directly above its representation. This means that matrices Fullchip and SS which are represented on top of the DRAM roofline (as are some of their reordered counterparts), have already highly optimized accesses to the vector elements, meaning that any further optimization is likely to yield small performance gains, and it might even result in the performance degradation, as can seen by the Fullchip RCM case. However, matrices represented below this point are able to benefit from the improved locality

<sup>&</sup>lt;sup>4</sup>Wai-Hung Liu and Andrew H. Sherman. "Comparative Analysis of the Cuthill–McKee and the Reverse Cuthill–McKee Ordering Algorithms for Sparse Matrices". *SIAM Journal on Numerical Analysis* 13.2 (1976), pp. 198–213. DOI: 10.1137/0713020.

<sup>&</sup>lt;sup>5</sup>Patrick R. Amestoy, Timothy A. Davis, and Iain S. Duff. "An Approximate Minimum Degree Ordering Algorithm". *SIAM Journal on Matrix Analysis and Applications* 17.4 (1996), pp. 886–905. DOI: 10.1137/S0895479894278952.

<sup>&</sup>lt;sup>6</sup>Richard J. Lipton, Donald J. Rose, and Robert Endre Tarjan. "Generalized Nested Dissection". *SIAM Journal on Numerical Analysis* 16.2 (1979), pp. 346–358. DOI: 10.1137/0716027.

<sup>&</sup>lt;sup>7</sup>Çatalyürek and Aykanat, "Patoh (partitioning tool for hypergraphs)".

<sup>&</sup>lt;sup>8</sup>Zhao et al., "Exploring Better Speculation and Data Locality in Sparse Matrix-Vector Multiplication on Intel Xeon".

<sup>9</sup>Davis and Hu, "The University of Florida sparse matrix collection".

**Figure 5** Real and Reordered Matrices represented in Sparse-CARM.

of the memory accesses to the vector elements, meaning that their performance can further be improved towards their respective roofline.

The same matrices and reordering algorithms were also tested in multi-threaded fashion (8 cores execution), with each thread being assigned a partition based on equal distribution of the rows with shared access to the X and Y vector. The representation of these matrices in the multi-threaded SpMV adapted CARM (see Figure 5b) show a similar trend to the single-thread experiments, since the reordering algorithms can either provide speedups or slowdowns depending on the matrix. However, some of these results are also highly dependent on load balancing of the multi-threaded execution. Since the experiments tested in this work focused on an even partition of the rows between threads, the number of non-zero elements computed by each thread may differ, resulting in data imbalance, thus provoking the performance degradation, as threads with less workload will idle at the end of their execution.

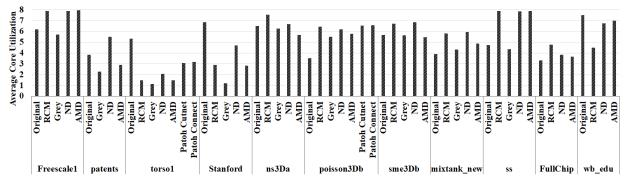

Figure 6 Average Core utilization for each used matrix in Multi-threaded execution.

By observing the average core utilization of each matrix and reordered versions, presented in Figure 6, it is possible to observe that reordering algorithms may result in an increase of the load balancing (all 8 cores are being utilized), while in others may provoke serious imbalance issues. For example, matrix Poisson3Db has an increase of the average core utilization from 3.5 to 6.4 when using RCM as a reordering algorithm. On the other hand, Torso1 has a reduction from 5.32 to 1.46 in the core utilization when using the same RCM algorithm. This explains their characterization in the Sparse CARM, since Poisson3Db has a speedup of 1.54x and Torso1 a slowdown of 0.26x. However, the performance impact of load balancing affects the insight provided by the Sparse CARM, as the variation of the representation of the matrices is no longer uniquely associated to an improvement in accessing the vector elements. To tackle this issue, the sparse-aware CARM analysis is extended in order to consider different core utilizations when targeting multi-thread execution.

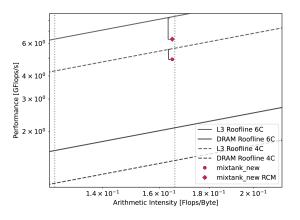

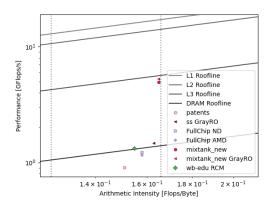

(a) Freescale1 and Freescale1 AMD represented with 6C and 8C rooflines respetively.

**(c)** Mixtank\_new and Mixtank\_new RCM represented with 4C and 6C rooflines respetively.

**(b)** *Stanford and Stanford ND with 7C and 5C rooflines respetively.*

(d) Torso1 and Torso1 RCM represented with 5C and 1C rooflines respetively.

**Figure 7** *Matrices and reordered versions represented with Sparse CARM rooflines according to their average core utilization.*

As can be seen in Figure 7, when the previously tested matrices are profiled in models that consider their average core utilization, it is possible to characterize the performance variations due to changes in locality of accesses to the vector elements, without the impact of load balancing. For example, the computation upon Freescale1, with an average core utilization of 6.2, and the AMD reordered version, with an improved load balancing reaching close to an average core

utilization of 8, when analysed using the VTune Top-down method, showcased no changes, indicating similar locality when accessing the vector elements, which was not fully corroborated by the 8 core sparse-aware CARM. However, when characterizing these matrices in sparse-aware models that consider their core utilization (Figure 7a), it is possible to verify that both Freescale1 and Freescale1 AMD are placed in the same relative position regarding the DRAM roof. This shows that there was no change in the main execution bottlenecks after reordering, which fully corroborates the findings of the Top-Down analysis.

Similar behaviour occurs for Stanford and Stanford ND, where VTune analysis indicates an improvement in the locality of the accesses to the vector elements, and comparing the representation of each kernel in Figure 7b relative to their rooflines, the reordered version is represented closer to the L<sub>3</sub> roofline, which corroborates the previous statement. For a scenario where the reordering lowers the locality of the accesses to the vector elements, the analysis of the Mixtank\_new and Mixtank\_new with RCM shows that the latter is placed at a lower relative position to their corresponding roofline compared to the original one, as can be seen in Figure 7c. The torso1 locality improvements showcased by the VTune analysis are also clearly seen in Figure 7d by the improved relative representation of the reordered matrix to its respective roofline.

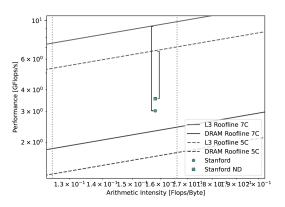

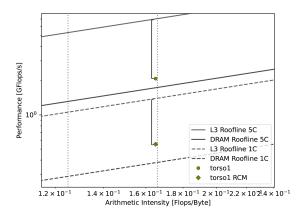

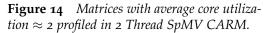

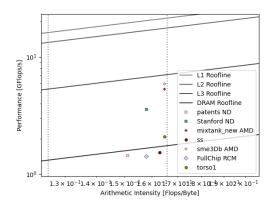

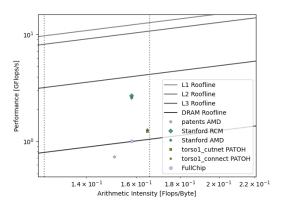

Figures 8, 9, 10, 11, 12, 13, 14 and 15 showcase all tested matrices and reordered counter parts represented on respective Sparse CARM models that correspond to their average core utilization. As can be observed, profiling the matrices in this manner, improves on the insight obtained from their representation related to the new rooflines. For example, observing the poisson3Db matrices represented in Figure 9, we can derive that the RCM reordering improved the locality of accesses to the vector elements when compared to the original matrix and the GrayRO reordered version, knowing that their representation is now less correlated to load balancing issues. The same analysis can be made between two reordered matrices, corresponding to different load balance scenarios, such as Stanford in Figure 9 and Stanford ND in Figure 11, in which the latter is positioned closer to its respective L3 roofline, showcasing a better scenario in terms of locality of accesses to the vector elements.

**Figure 8** *Matrices with average core utilization*  $\approx$  8 *profiled in 8 Thread SpMV CARM.*

**Figure 9** *Matrices with average core utilization*  $\approx$  7 *profiled in 7 Thread SpMV CARM.*

Based on these results, in order to profile the use of the available computational power when executing the SpMV computation upon matrices in multi-threaded fashion while also excluding the load balancing issue, each case should be profiled according to their respective average core utilization, so as to isolate the cache locality as the major performance impediment and assess whether further optimization on the matrix structure through reordering is necessary or even

**Figure 10** Matrices with average core utilization  $\approx$  6 profiled in 6 Thread SpMV CARM.

**Figure 12** Matrices with average core utilization  $\approx$  4 profiled in 4 Thread SpMV CARM.

**Figure 11** *Matrices with average core utilization*  $\approx$  5 *profiled in* 5 *Thread SpMV CARM.*

**Figure 13** *Matrices with average core utilization*  $\approx$  3 *profiled in* 3 *Thread SpMV CARM.*

**Figure 15** *Matrices with average core utilization*  $\approx$  1 *profiled in 1 Thread SpMV CARM.*

worth the pre-processing considering the maximum attainable performance. With this, the multi-threaded performance model offers additional insights on where the optimization process should focus. For example, if a specific matrix is represented on top of a memory roof that corresponds to its average core utilization, the next optimization step should focus on improving the load balancing if the average core utilization is less than the total number of cores (maximum core utilization). If the application has good core utilization but is below the roof right above its representation, then reordering techniques can be applied to improve the accesses to the vector elements. Finally, in the case of a kernel that is represented below the memory roof in a model that does not correspond to its maximum core utilization, further optimization can be focused on both the accesses of the vector elements and load balancing.

## 2.1.4 ENERGY EFFICIENCY ANALYSIS AND OPTIMIZATION

Focusing on power consumption and energy-efficiency of sparse computation, we also provide herein a roofline-based analysis according to the benchmarking methodology presented in Deliverable 4.2. With this aim, an evaluation of the variation of performance, power consumption and energy-efficiency according to the AI of the kernel, *i.e.*, the Number of Non-Zeros (NNZ) per row of the input matrices, is performed.

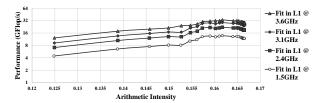

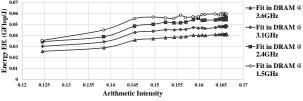

**Figure 16** *Performance variation according to Core Frequency when all data fits inside* L1 *cache.*

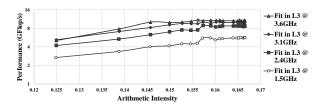

**Figure 18** *Performance variation according to Core Frequency when all data fits inside* L<sub>3</sub> *cache.*

**Figure 17** *Performance variation according to Core Frequency when all data fits inside L2 cache.*

**Figure 19** *Performance variation according to Core Frequency when all data fits inside DRAM.*

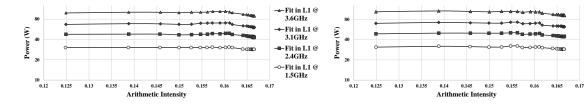

In order to explore possible optimization options to improve the energy efficiency for SpMV computation, the micro-benchmarking procedure proposed in Deliverable 4.2 was executed with lower core frequencies, exercising the possible AI ranges of the x86 assembly kernel. Figures 16, 17, 18 and 19 showcase how the performance is negatively affected by lowering the core frequency. For the cache levels closest to the core, such as L1 and L2, the decrease in performance is proportional to the frequency decrease, since these memory levels operate at the same speed as the core. For example, the performance loss measured between the maximum performance tests using 3.6GHz and 1.5GHz (a 58.2% decrease), was 58.6% (from 33.42 to 13.85 GFlop/s) and 58.5% (from 28.10 to 11.65 GFlop/s) for L1 and L2 respectively. For the L3 and DRAM focused testing, the relative performance decrease is lower than the one obtained for the private caches, due to the separate frequency domains at which both these memories work. For example, the performance

loss measured between maximums from testing performed in each of the memory levels, when lowering the frequency from 3.6GHz to 1.5GHz (58.23% frequency drop), was 48% (from 10.96 to 5.7 GFlop/s) and 17.1% (from 2.68 to 2.22 GFlop/s) for L3 and DRAM respectively.

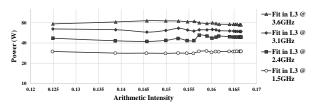

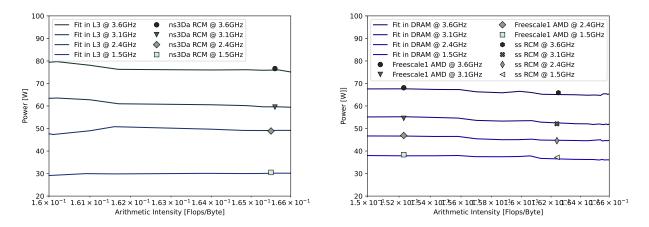

Regarding the effects of frequency scaling to the power consumption, it is possible to observe in Figures 20, 21, 22 and 23, that differently from performance, the decrease in power consumption is lower than the ratio between frequencies. For example, the maximum power loss when lowering the frequency from 3.6GHz to 1.5GHz is 29.7%, 30.2%, 35.5% and 55.9% for L1, L2, L3 and DRAM focused tests respectively. Moreover, it is possible to verify that for lower frequencies, the power consumption of the Dynamic Random Access Memory (DRAM) focused tests is higher than the ones obtained for the remaining memory levels, as the former averages 36.8 W and for example, the L1 test averages 29.49 W, which is likely correlated to the fixed frequency at which the external memory works. In this scenario the power consumption in the package domain gets dominated by the active components in the memory controller instead of the other memory levels which are working at a very low frequency.

**Figure 20** *Power variation according to Core Frequency when all data fits inside L1 cache.*

**Figure 22** *Power variation according to Core Frequency when all data fits inside L*<sub>3</sub> *cache.*

**Figure 21** *Power variation according to Core Frequency when all data fits inside L2 cache.*

-Fit in L2 @ 3.6GHz

←Fit in L2 @

3.1GHz

➡Fit in L2 @

->-Fit in L2 @ 1.5GHz

2.4GHz

**Figure 23** *Power variation according to Core Frequency when all data fits inside DRAM.*

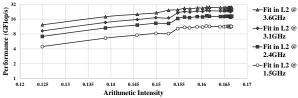

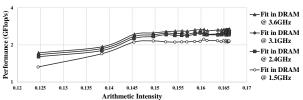

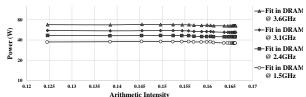

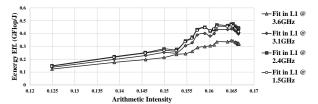

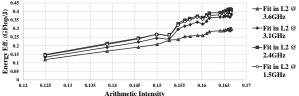

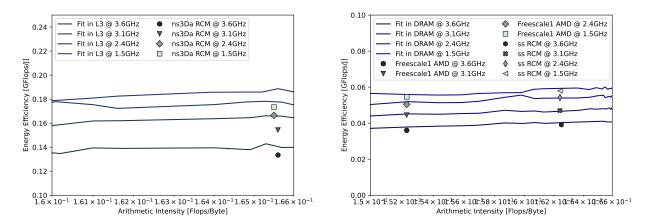

Figures 24, 25, 26 and 27 showcase the variation of energy efficiency according to the AI when tested with different core clock speeds. As it can be observed, it is possible to attain better energy efficiency when lowering the frequency, due to higher reduction in power consumption than the one that occurs in performance. In particular for L1 and L2 caches (Figures 24 and 25), there is an increase in the maximum efficiency of 35.2% and 32.3% respectively when lowering the core frequency from 3.6 GHz to 2.4GHz. However, when further reducing the frequency from 2.4GHz to 1.5GHz, there is a slight decrease in the efficiency, showcasing that for the L1 and L2 caches, the minimum frequency is not coupled with the maximum efficiency. On the other hand, L3 and DRAM tests (shown in Figures 26 and 27), indicate that reducing the frequency from 3.6GHz to 1.5GHz, the energy efficiency. For example, when decreasing the frequency from 3.6GHz to 1.5GHz, the energy efficiency increases 46% and 32.4% respectively. However for lower AI values, tests fitting inside L3 show diminished returns in lowering the clock speed until 1.5GHz

as testing using 2.4GHz returns the highest efficiency values in this range.

**Figure 24** *Energy Efficiency variation according to Core Frequency when all data fits in L1 cache.*

**Figure 25** *Energy Efficiency variation according to Core Frequency when all data fits in L2.*

**Figure 26** Energy Efficiency variation according to Core Frequency when all data fits in L<sub>3</sub>.

**Figure 27** Energy Efficiency variation according to Core Frequency when all data fits in DRAM.

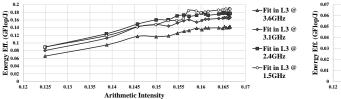

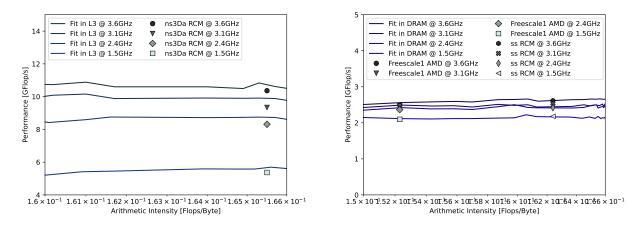

In order to verify the applicability of this roofline-based analysis to the optimization of power consumption and energy efficiency, some of the previously tested real matrices were evaluated by considering the performance, power consumption and energy-efficiency curves with varying core frequencies. To simplify the analysis, the selected matrices have almost perfect load balancing, with core utilization being close to the maximum cores used. Nevertheless, this analysis can be easily applied to imbalanced matrices by extending the micro-benchmarking methodology from Deliverable 4.2 to different number of threads. Figures 28, 29 and 30 present the analysis of performance, power and energy efficiency respectively, of Freescale1 AMD, ss RCM and ns3Da RCM for different core frequencies, by relying on the curves obtained for the memory levels which limit their performance.

The performance and power variation (seen in Figures 28 and 29) in the computation of the matrices presents a very similar behaviour regarding the relative loss compared to the previous tests throughout the AI range of the kernel. As can be seen, the performance drop is less noticeable for the matrices limited by the DRAM compared to the other matrix which was able to be stored inside the L<sub>3</sub> cache, due to the DRAM frequency remaining unchanged. Likewise, analysing the power variation, all tested matrices reach similar values in the same AI of the curves.

When observing the energy efficiency variation (presented in Figure 30), for all of the tested matrices, lowering the core frequency increases energy efficiency. Furthermore, the matrices that are focused on DRAM, Freescale1 AMD and ss RCM, are placed very close to the perceived best cases for energy efficiency for any of the tested frequencies, meaning that improving their efficiency was only attained by lowering the clock speed of the core.

The portrayed scenario indicates that in situations where optimizing for energy efficiency is more important than improving performance, lowering the core clock frequency is a simple method to further increase the efficiency of the SpMV computation. Looking back at the multithreaded testing performed in real matrices, the Freescale1 and AMD reordered version (as seen

Figure 28 Variation in Performance of SpMV applied to real matrices when changing core frequency.

Figure 29 Variation in Power consumption of SpMV applied to real matrices when changing core frequency.

**Figure 30** Variation in Energy Efficiency of SpMV applied to real matrices when changing core frequency.

in Figure 7a) showcase a scenario where the memory accesses to the vector elements are already highly optimized, given their relative position to the corresponding roofline, providing a perfect scenario where lowering the clock speed of the processor, with little change in overall execution time, can increase the energy efficiency of the computation.

## 2.2 ROOFLINE-BASED HARDWARE SCALING FOR EFFICIENT SPARSE COMPUTING

The demand for efficient computing systems has seen a recent increase with the end of Dennard's scaling and Moore's law. In response to this challenge, the RISC-V instruction set architecture (ISA) has emerged as a promising solution. RISC-V is based on Reduced Instruction Set Computing (RISC) principles, which have gained significant popularity in both small battery powered systems and high-performance computing. Its open-source nature and lack of licensing requirements have also led to its rapid growth in adoption, both in the academic and commercial spaces. Performance analysis and modelling tools are crucial for an emerging architecture such as RISC-V, as it enables software to better leverage architectural resources, and aids in designing efficient hardware that meets application demands.

To this end, a hand-optimized SpMV implementation in RISC-V assembly is presented, which is then used to do performance analysis on a simulated RISC-V architecture. The cache dynamics of SpMV execution are explored, identifying ways the hardware may be scaled to improve performance. Through the use of the Cache-Aware Roofline Model, the algorithm's range of arithmetic intensities is analyzed, aiding in the hardware design process through the identification of application demands and bottlenecks.

## 2.2.1 SPMV IMPLEMENTATION

The proposed SpMV implementation operates on Compressed Sparse Row (CSR) format matrices, with the matrix and vector being composed of 64-bit floating-point values, while the row offset and column index arrays use 32-bit integers. The optimized implementation relies on the unrolling of the inner loop that iterates through the elements in one row, with an unrolling factor of 8. When iterating through the elements in each row, the number of remaining non-zero values is determined, and used to calculate a target jump address. If 8 or more values remain, the execution jumps to the start of the unrolled section. If there are fewer than 8 values remaining, the program jumps within the unrolled portion so that as many elements as remaining are processed.

## 2.2.2 ARCHITECTURE AND METHODOLOGY

The aforementioned implementation was tested using gem5,<sup>10</sup> a computer architecture simulator with a number of parameterizable CPU models. The Minor CPU, an in-order model with a four-stage pipeline is used, initially parameterized with a 32kB L1 cache with 4 ways, and a 128kB L2 cache, both with 64 byte lines, running at 2GHz.

## 2.2.3 EXPLORING CACHE DYNAMICS

In order to explore the performance impact the caches have on the execution, two synthetic sparse matrices were generated, referred to as the best- and worst-cases. Both matrices are of size (D, D) where D is the number of 8 byte elements that the L1 cache plus an extra line can contain, in this case 4104. The matrices are given this size so that the vector does not entirely fit in the L1 cache, which allows dynamics such that the reuse of the vector's data and cache eviction to be explored.

<sup>&</sup>lt;sup>10</sup>Jason Lowe-Power et al. "The gem5 Simulator: Version 20.0+". en. *arXiv:2007.03152* [*cs*] (2020). arXiv: 2007.03152. URL: http://arxiv.org/abs/2007.03152 (visited on 12/28/2021).

The worst-case matrix aims to make no reuse of the vector data stored in the L1 cache, evicting previously cached data with every access. Since the L1 cache is 4-way associative, 5 accesses to distinct addresses mapping to the same cache line must be made in order to evict the vector's previously cached data. As the 32kB L1 cache has 8kB per set, and we are indexing a vector of 64-bit or 8 byte elements, the column indexes of each row are generated at an increment of 1024, leading to 5 accesses mapping to the same cache address per row. In other words, each row of the spare matrix contains 5 non-zero elements, spaced 1024 columns apart. This causes the desired eviction on every access of the vector, ensuring it is not stored in the L1 cache.

The best-case matrix has the opposite goal, which is maximizing the reuse of cached data. In order to better establish a direct comparison, the number of accesses per row is maintained constant, i.e., the number of non-zero elements per row is still 5. However, the column indexes of these non-zero elements instead allow for contiguous access to the elements of the vector. Since each 64 byte cache line can contain 8 elements of the vector, each read always accesses the same cache line, which should be cached in L1 after the very first element is read. This way there is maximal data reuse, given the accessed vector elements are always in the L1 cache after the first read.

The two matrices are processed, with their properties and performance results shown in Table 2. As expected, the best-case matrix significantly outperforms the worst-case matrix in performance, despite the two differing exclusively in the column indexes. This highlights the cache's impact on performance, even when it is impossible to cache the entire set of data.

|                       | Worst-case   | Best-case    |

|-----------------------|--------------|--------------|

| Dimensions            | (4104, 4104) | (4104, 4104) |

| NNZ                   | 20520        | 20520        |

| FLOP                  | 45144        | 45144        |

| Bytes                 | 459652       | 459652       |

| Performance (GFLOP/S) | 0.072        | 0.119        |

**Table 2** Properties and performance of the best- and worst-case matrices

In order to mitigate the issues with cache eviction seen in the worst-case scenario, the architecture is reparametrized with two approaches, altering the L1 cache's dimensions and its associativity. Both matrices are processed in the new architecture, with the results presented in Table 3. As illustrated by the results, both modifications of the cache achieve the same result, fully mitigating the decrease in performance seen in the worst-case matrix, as cache eviction is prevented and the vector is stored in the L1 cache for both cases.

|                                     | Size = 48kB | Associativity = 8 |

|-------------------------------------|-------------|-------------------|

| Worst-case performance<br>(GFLOP/S) | 0.119       | 0.119             |

| Best-case performance<br>(GFLOP/S)  | 0.119       | 0.118             |

Table 3

Performance of the best- and worst-case matrices following changes to the L1 cache

While both changes result in nearly the same performance, it should be noted that they would differ significantly in resource usage when implemented. Depending on the power and area budgets of the design, a designer might prefer the increase in associativity for its much more modest resource usage. It is also of note that the synthetic nature of the two matrices may lead to

the results not translating fully to real data – if accesses to the vector are not sufficiently sparse, an increase in associativity may not be sufficient to fully mitigate cache evictions, in which case an increase of the cache size may be necessary for optimal performance.

### 2.2.4 EXPLORING THE RANGE OF ARITHMETIC INTENSITIES

By analysing the presented SpMV implementation, it is possible to determine the number of floating-point operations performed and bytes transferred during execution from the characteristics of the matrix. With these, it is possible to calculate the arithmetic intensity of the workload as follows:

$$AI = \frac{FLOPs}{bytes} = \frac{R + 2 \cdot nnz}{4 + 20 \cdot nnz + 12R'}$$

(1)

where *R* represents the number of rows and *nnz* the number of non-zero values of the matrix. By manipulating and simplifying the expression, we can determine the arithmetic intensity exclusively as the ratio between non-zero values and rows, such that:

$$AI = \frac{2\frac{nnz}{R} + 1}{\frac{4}{R} + 20\frac{nnz}{R} + 12} \approx \frac{2\frac{nnz}{R} + 1}{20\frac{nnz}{R} + 12}, \text{ when } R >> 1.$$

(2)

By defining the limits of the aforementioned ratio, we can determine the range of arithmetic intensities achievable. For the sake of applicability, the minimum ratio is limited to 1, thus the matrices with empty rows are excluded from this analysis. Since there is no upper limit to the ratio of non-zeros and rows, it can be concluded that the range of arithmetic intensities covered by the adopted SpMV kernel is  $\left[\frac{3}{3^2}, \frac{1}{10}\right]$ . It is possible to create a matrix exhibiting any arithmetic intensity within this range by selecting the ratio between the number of rows and the number of non-zero values.

In this vein, two sets of matrices of varying arithmetic intensities and sizes are created, following the same principles as the previously presented best-case matrix. Table 4 shows the characteristics of each set of matrices, the "L1 set" and "L2 set", named after the cache level they target.

|                  | L1 set | L2 set |

|------------------|--------|--------|

| Target Size (kB) | 24     | 64     |

| NNZ              | 1228   | 3276   |

| Columns          | 614    | 1638   |

Table 4

Characteristics of the two sets of matrices

As all matrices in each set share the same number of non-zero values and columns, the change in the  $\frac{nnz}{R}$  ratio (which governs the arithmetic intensity) is achieved by varying the number of rows. The non-zero values are evenly distributed among the rows for optimal uniformity, with matrices that have fewer rows becoming more dense.

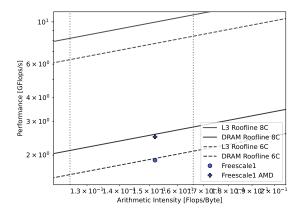

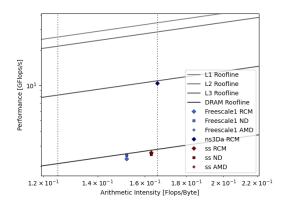

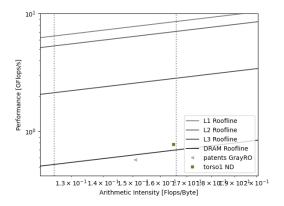

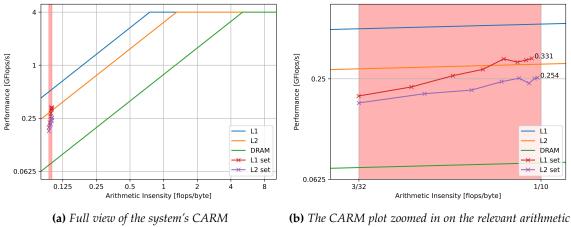

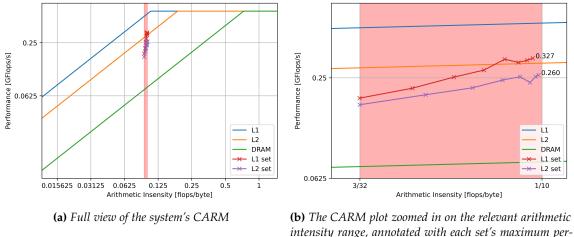

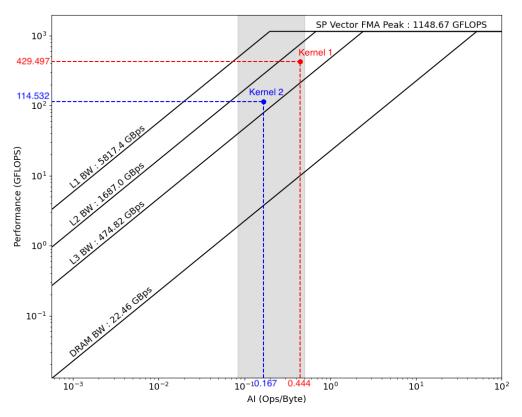

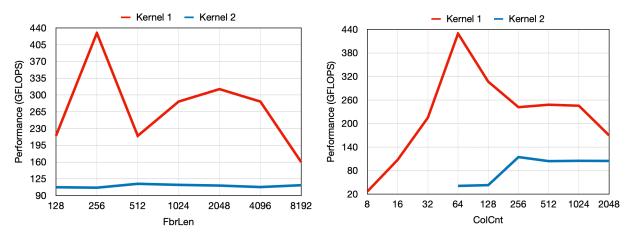

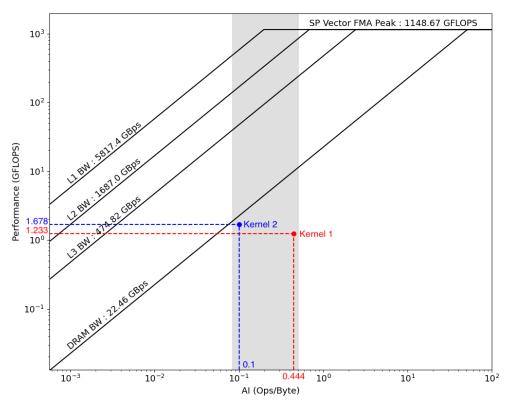

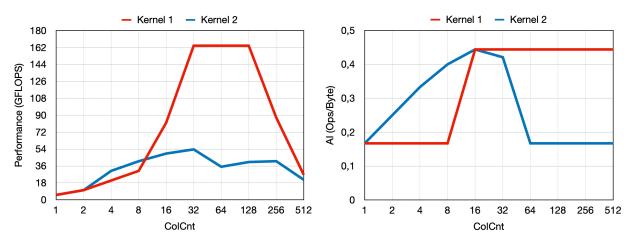

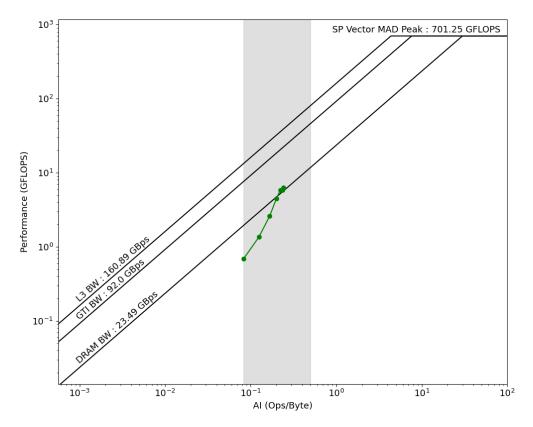

The system is first benchmarked in order to build its Cache-Aware Roofline Model, after which the sets of matrices are processed. Each matrix is processed twice in order to level the cache data and obtain steady-state performance figures (closer to the CARM's rooflines), which are measured during the second execution. Figure 31 shows the architecture's CARM, along with the performance of both sets plotted on it.

The results of both sets show an increase in performance as the arithmetic intensity increases, consistent with what is expected due to the memory-bound nature of the range in study. The set targeting the L1 cache is capable of delivering a higher performance than the one targeting the L2

intensity range, annotated with each set's maximum performance

Figure 31 Performance of the two matrix sets plotted on the system's CARM

cache, as expected due to the higher L1 bandwidth, and resulting higher roofline. However, it is clear both performance curves are positioned significantly below their theoretical maximums, i.e., their respective rooflines. One of the reasons for this behaviour lies in the in-order nature of the processor, which execution paradigm differs from CARM's assumption that memory and floating-point operations execute in parallel. Additionally, the algorithm is significantly more complex than the synthetic benchmarks used to measure the memory bandwidth and peak performance with which the CARM is built, with other dynamics at play such as frequent conditional branching and data dependency. Despite the results not fully correlating with the model, the CARM can still be used to expeditely determine the performance upper limits of the arithmetic intensity range being operated in.

# 2.2.5 IMPROVING SPMV EFFICIENCY WITH ROOFLINE-BASED ARCHITECTURE SCALING

In this part of the study, we focus on exploring the possibility of improving the SpMV efficiency by following the hardware utilization insights given by the CARM. In a nutshell, we aim at scaling the capability of different hardware resources in order to meet the demands of the application. While in the analysis of cache dynamics the goal was the improvement of performance through the reparameterization of the cache, the objective now is to scale down the architecture to reduce the hardware's footprint, while maintaining a similar performance level.

As Figure 31a shows, the SpMV kernel is positioned deeply in the memory-bound region, and the attainable AIs range is very limited (see transparent shaded region), meaning this kernel will never be able to exploit the compute upper-bounds of this architecture (see the distance from the horizontal roof). Given these observations, the peak (compute) performance can be significantly reduced while the current performance (limited by memory bandwidth) can be kept, scaling the architecture to closely meet the application requirements. In this study, this scaling is achieved by replacing the floating-point unit with a non-pipelined implementation, where the unit's latency and its effect on performance is explored.

With the insights provided by the CARM, it is possible to determine the latency that minimizes the peak performance, while not reducing the attainable performance at a desired arithmetic intensity. Equation 3 describes the attainable performance according to the CARM, where B is the bandwidth of the memory level in study, I is the arithmetic intensity, and  $F_p$  is the peak

performance.

$$F_{a}(I) = \min\{B \cdot I, F_{p}\}$$

(3)

By setting a goal of preserving the performance across all memory levels at the upper limit of the arithmetic intensity range, we consider the memory level with the highest bandwidth, the L1 cache. Given that the range in study is memory-bound, the attainable performance is governed by the equation's left term, and we may calculate as (4):

$$F_{a}(\frac{1}{10}) = B_{L1 \to C} \cdot \frac{1}{10} = 0.532 \text{ GFLOP/s}$$

(4)

We may then determine the maximum latency that results in a peak performance above this result (4) using Equation 5, where  $F_{po}$  denotes the system's original peak performance of 4 GFLOP/s:

Latency = ceil(

$$\frac{F_{po}}{F_{\alpha}(\frac{1}{10})}$$

) = 7 cycles (5)

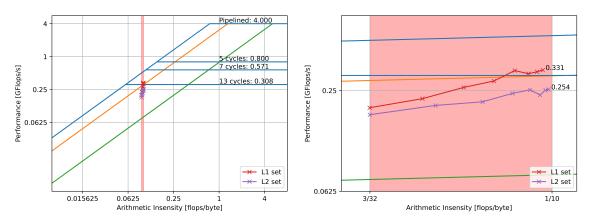

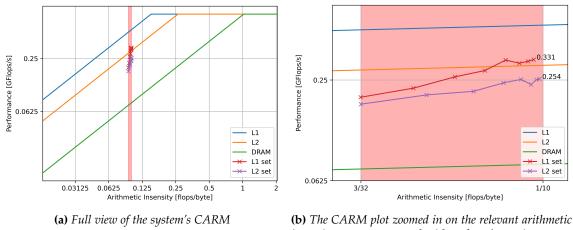

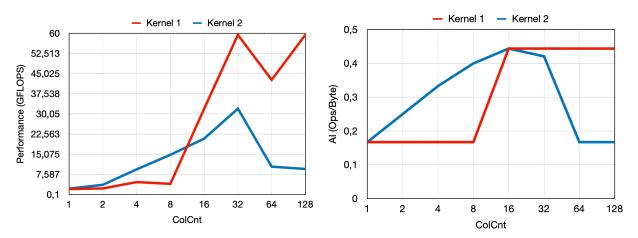

Two more latency values are tested in order to better study this parameter's impact on performance, these being 5 and 13 cycles. The former was chosen to provide a higher peak performance, while the latter was obtained by performing the process shown in Equations 4 and 5 for the L2 cache's bandwidth. The resultant rooflines, along with the original one, and the SpMV performance of the original system are presented in Figure 32.

(a) Full view of the CARM resulting from each of the la- (b) The CARM plot zoomed in on the relevant arithmetic tencies, annotated with the respective peak performance

intensity range, annotated with each set's maximum performance

**Figure 32** Comparison between the rooflines of the 4 parameterizations and the SpMV on the original system

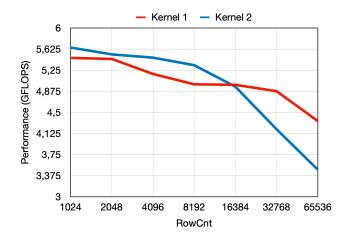

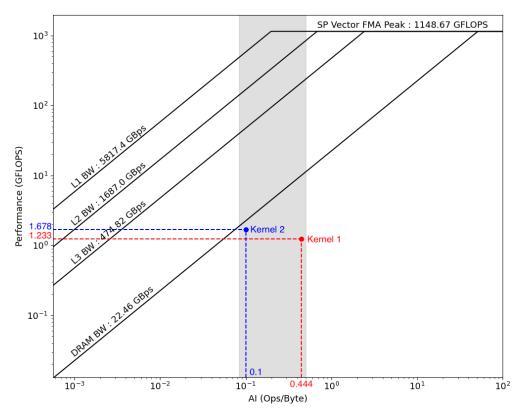

As predicted, the ridge points of the 7-cycle system's L1 roofline and of the 13-cycle system's L2 roofline are immediately to the right of arithmetic intensity range's upper limit, preserving the respective performance upper-bounds. The compute-bound roof of the 13-cycle system is lower than the observed SpMV performance on the original system, and as such a drop in performance is expected. The SpMV performance is then measured on each of the systems, with the results shown below, beginning with the 7-cycle system in Figure 33.

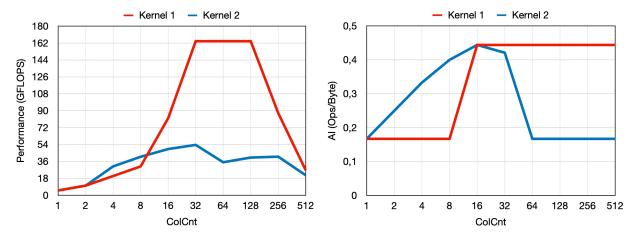

As demonstrated by the results, despite the significant reduction to the system's peak performance, from 4 GFLOP/s to approximately 0.571 GFLOP/s, the performance of SpMV remains virtually unchanged. By determining the ratio between the achieved performance and the peak performance, we can evaluate if efficient usage of the hardware's resources is being made. In the

formance

**Figure 33** *Performance of the two matrix sets plotted on the system's CARM after the floating-point unit's reparameterization to a 7-cycle latency*

case of the L1 set, while in the original system the execution reaches 8.3% of the peak performance, the reparameterization increases it to 57.3%, bringing the architecture's capabilities much closer to the requirements.

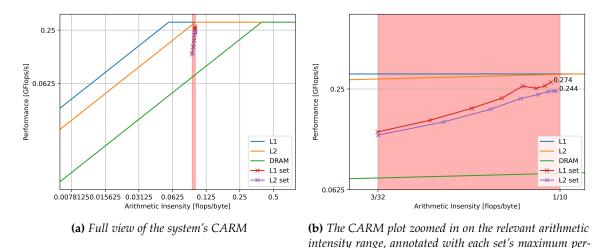

The 5-cycle system is then tested, with the outcome presented in Figure 34. This results in a higher peak performance when compared to the 7-cycle reparameterization, at o.8 GFLOP/s, and similarly it does not affect the SpMV performance. However, this also leads to a less efficient use of resources, with the ratio between achieved and peak performance sitting at 40.9%.

**(b)** The CARM plot zoomed in on the relevant arithmetic intensity range, annotated with each set's maximum performance

**Figure 34** *Performance of the two matrix sets plotted on the system's CARM after the floating-point unit's reparameterization to a 5-cycle latency*

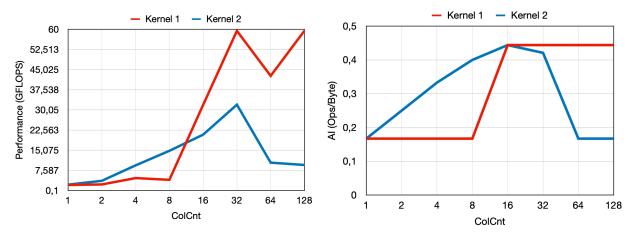

Lastly, the 13-cycle system is evaluated, with the results shown in Figure 35. The system now attains a peak-performance of 0.308 GFLOP/s, which is lower than the originally achieved performance of the L1 set. Consequently, this leads to a reduction in this set's performance by approximately 17.2%, as it is no longer able to benefit from the the L1 cache's high bandwidth. With the sharp reduction in peak-performance, the execution becomes bottlenecked by the floating-

point unit, bringing it closer to the L2 set. Despite the L2 set originally performing below the L2 roofline, a slight reduction in performance of 3.9% is also observed. This demonstrates some level of reuse of L1 data in this set, despite the performance in the original system staying below the L2 roofline. As explained previously, elements of the vector may be cached in L1 even if the entirety of the dataset does not fit in it, leading some sections of the algorithm benefiting from a higher memory bandwidth, and achieving higher performance due to their memory-bound nature. By reducing the peak performance, those sections instead become compute-bound.

**Figure 35** *Performance of the two matrix sets plotted on the system's CARM after the floating-point unit's reparameterization to a 13-cycle latency*

formance

While experimental results are not available, we can speculate about the power consumption of the new floating-point unit, comparing the original system with the first reparameterization, which has lowest-performing, presumably most efficient floating-point unit that does not harm SpMV performance. Seeing as the unit is no longer pipelined and has a 7-cycle latency, its input frequency is reduced by a factor of 7. This reduction is likely to provide a significant increase in energy efficiency due to the strong correlation between a digital circuit's power consumption and its frequency.

Other approaches to reduce the peak performance are available, such as providing the caches and the core with different clocks, and reducing the clock frequency of the latter, which would likely lead to a significant decrease in power consumption in the whole core. It should be noted that this may have a more pronounced negative impact on performance in this particular case, given that the execution is not exclusively limited by the memory system, and the reduction in processor frequency may exacerbate the slowdowns caused by branching and data dependency.

## 2.2.6 CONCLUSION

Overall, the results demonstrate the pronounced impact the processor's cache has on performance, particularly due to the memory-bound nature of the workload, which is evidenced with the aid of the CARM. Through an analysis of the algorithm's arithmetic intensity range, insights provided by the CARM allowed for an informed redesign of the architecture, leading to more power efficient execution. This study demonstrates the key role a performance modeling tool such as the CARM can play in hardware design, allowing the architecture to be tailored to the requirements of any workload, and improving the overall efficiency.

# 3 EXPLORING THE PROCESSING LIMITS OF SPMM AND TTM ON CPU/GPU SYSTEMS

## 3.1 ANALYSIS OF SPARSE MATRIX MULTIPLICATION ON A GPU DEVICE

SpMM kernels, which perform matrix multiplication between a sparse matrix and a dense matrix, are widely used in High Performance Computing (HPC) scientific and engineering applications. The processing of sparse matrices provides advantages such as requiring less storage space and the fact that computations can in some cases be performed significantly faster than with their dense counterparts. This is, respectively, the result of not storing (any or all of) the zero elements and only needing to compute with the non-zero elements of the sparse input matrix.

Modern accelerator devices such as Graphics Processing Units (GPUs), which are widely used as accelerators for both dense and sparse matrix multiplication kernels, provide Dynamic Voltage and Frequency Scaling (DVFS) capabilities to comply with power constraints and increase energy efficiency. Depending on the application load, different frequencies can be selected on-the-fly for the accelerator compute and memory components. These can be set independently to exploit workload characteristics. Particularly important is the amount of computations in relation to global memory loads/stores. For some compute-bound workloads it might be preferable in terms of power and energy efficiency to lower memory clocks while keeping core clocks high. In contrast, for memory-bound workloads, one might lower core clocks with no significant effect on performance.

In some cases, the use of SpMM kernels can exercise the available compute and memory resources differently than GEMM kernels. While the latter is typically compute-bound, and as a result often used as a benchmark to show peak performance of parallel accelerator devices, operations involving sparse matrices can be memory-bound to varying degrees. As a result, given an hardware platform or device, the optimal core and memory frequencies can depend on the representation format or algorithm used, on the particular inputs, i.e. matrix dimensions, sparsity/density levels (number of zeros to non-zeros, or vice-versa), and on the numerical precision used and hardware support for native efficient operation at the used precision.

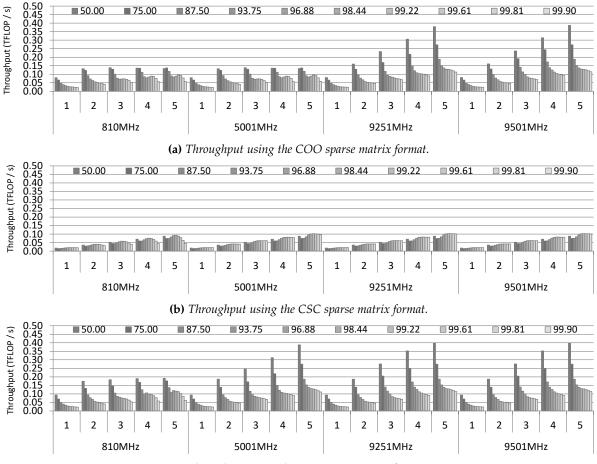

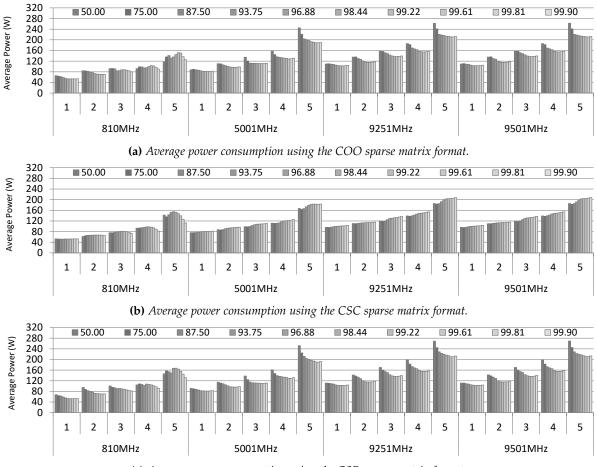

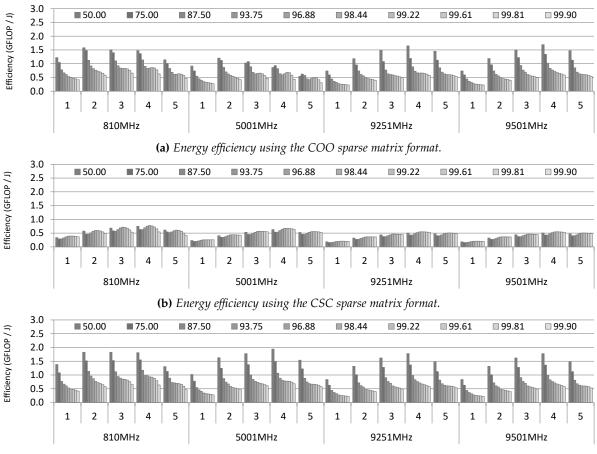

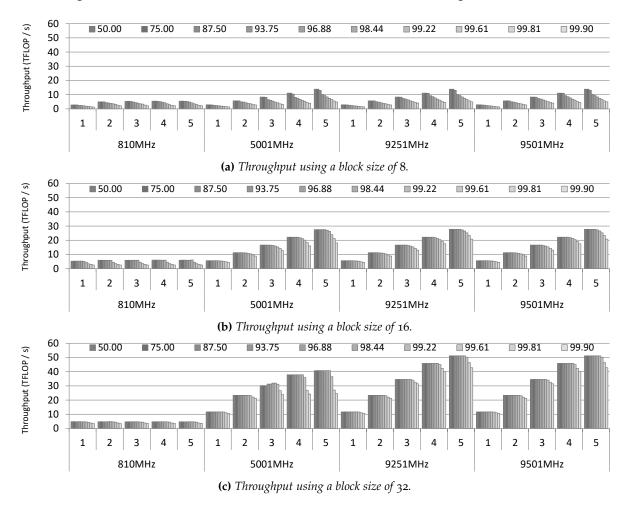

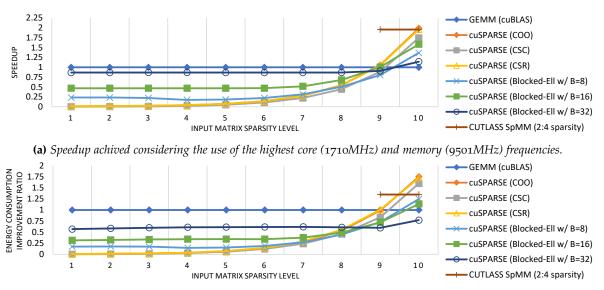

We evaluate the potential of tuning the core and memory frequencies of an Ampere GPU accelerator device for optimizing the execution of SpMM (and GEMM). Cross-comparing between the use of different methods for multiplying sparse matrices, we analyse the effect of GPU core and memory frequencies on the achieved throughput, average power and energy efficiency (and resulting energy consumption), taking into account inputs with different sparsity/density levels, the use of different matrix representation formats, and the use of 32-bit (float) or 16-bit (half) floating-point precision for data representation.

## 3.1.1 TARGETED DEVICE, REPORTED METRICS AND EXECUTION VARIABLES

**Targeted device.** All experiments have been performed on an Intel Core-i7 system with an NVIDIA RTX 3080 Ampere (10GB / GA102-200-KD-A1 variant) GPU accelerator. The targeted GPU has 64 Streaming Multiprocessors (SMs) 8704 CUDA cores (128 per SM) and 272 tensor cores (4 per SM). The GPU has a base core frequency of 1440 MHz and a boost core frequency of 1710 MHz. In the Ampere architecture, each CUDA core is capable of performing a native 32-bit (or 16-bit) fused-multiply add operation per clock cycle (1:1 FP16 to FP32 ratio). Thus, on the targeted GPU, the peak floating-point throughput on CUDA cores (calculated at boost frequency) is 29.77 TFLOP/s (=  $8704 \times 1710 \times 2$ ). On the Ampere GA102 GPU microarchitecture, each tensor core performs 64 fused multiply-add 16-bit floating-point operations with 32-bit

accumulation, totaling in a throughput of 59.54 TFLOP/s (=  $64 \times 272 \times 1710 \times 2$ ) considering the use of the whole device. Global memory is of the GDDR6X type and can go up 1188MHz (19 Gbit/s effective speed), reported as 9501MHz in the NVIDIA System Management Interface (nvidia-smi) command line utility, due to this type of memory sending 8 bits of data per clock cycle (quad data rate and PAM4 signaling). The bandwidth to global memory is 760.3 GB/s. All experiments have been performed relying on CUDA 12.0 and GPU Driver version 525.85.12.

**Reported Metrics.** We report the achieved throughput in Tera FLoating-point Operations Per Second (TFLOP/s) and the average power consumption in Watts (W). Throughput is calculated based on the execution time of the given matrix multiplication run and on the actual number of performed floating-point operations. Time measurements are performed relying on the absolute elapsed wall-clock time for executing matrix multiplication on the GPU, being obtained on the host with clock\_gettime(CLOCK\_MONOTONIC, &time). Power measurements are performed relying on the NVIDIA Management Library (NVML), an API for monitoring and managing NVIDIA GPUs. Energy efficiency, which is calculated from the previous metrics, is reported in Giga FLoating-point Operations Per Joule (GFLOP/J). Notice that the cost of populating the input matrices, converting to/from matrix formats, or any other host code preceding/following the execution of matrix multiplication routines on the GPU are not taken into account in the performance, power and energy efficiency metrics. There is a minimum warm-up period of 5 seconds before any measurement is performed, which is accomplished by running the matrix multiplication kernel under study as many times as needed. Multiple executions are also performed during the measurement phase to increase the precision of the reported metrics. After the warm-up period, on the measuring phase, the kernel is again executed for a minimum time of 5 seconds, being the execution time for a single kernel execution estimated by dividing the elapsed time by the amount of kernel executions.

**Execution Variables.** We use the cuBLAS<sup>11</sup> and cuSPARSE<sup>12</sup> libraries for performing matrix multiplication targeting CUDA cores and (dense) tensor cores. These are the defacto libraries for GEMM and SpMM (and related) computations on NVIDIA GPUs. The versions used are those included in the CUDA software stack, being the default versions of the algorithms of each of these libraries the ones for for the experiments. Native hardware-accelerated SpMM is performed relying on CUTLASS<sup>13</sup> (version 2.11), which is a set of CUDA C++ abstractions for implementing matrix-multiplication and related computations. CUTLASS supports the Sparse Matrix Multiply-Accumulate (MMA) Ampere tensor cores, which cuBLAS and cuSPARSE do not.

To evaluate the impact frequency scaling, we performed runs with different GPU core and memory frequencies, set through the nvidia-smi tool before execution of a CUDA program performing matrix multiplication. For the GPU core we alternatively use a frequency of 345MHz, 690MHz, 1020MHz, 1365MHz or 1710MHz, which are the closest supported frequencies to 20%, 40%, 60%, 80% or 100% of the vendor-announced boost frequency. Memory is set alternatively to 810MHz, 5001MHz, 9251MHz or 9501MHz, the four highest frequencies supported by the driver.

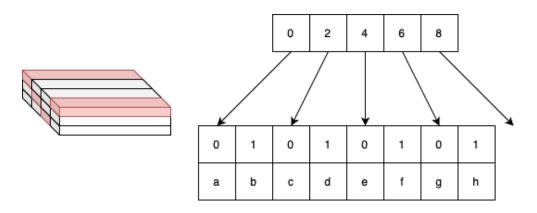

As the starting point for all experiments, we rely on dense representations for representing both input matrices. For SpMM runs, the first matrix input is converted to a sparse representation at runtime. In the experiments using cuSPARSE to perform SpMM, we consider the Coordinate (COO), Compressed Sparse Column (CSC), CSR and Blocked-Ellpack (Blocked-ELL) formats,

<sup>&</sup>lt;sup>11</sup>NVIDIA Corporation. *cuBLAS*. version 12.0. 2023. URL: https://developer.nvidia.com/cublas.

<sup>&</sup>lt;sup>12</sup>NVIDIA Corporation. *cuSPARSE*. version 12.0. 2023. URL: https://developer.nvidia.com/cusparse.

<sup>&</sup>lt;sup>13</sup>Andrew Kerr et al. CUTLASS. version 2.11.0. 2022. URL: https://github.com/NVIDIA/cutlass.

which are the formats supported for representing sparse matrices in this library. The experimental campaign considers the following different sparsity levels: ~ 50.00%, ~ 75.00%, ~ 87.50%, ~ 93.75%, ~ 96.88%, ~ 98.44%, ~ 99.22%, ~ 99.61%, ~ 99.81%, ~ 99.90%.

In the experiments using the CUTLASS library for sparse tensor-core accelerated SpMM, we use specially built matrices complying with the 2:4 fine-grained sparsity format. This format represents the first input matrix (the sparse matrix) as two smaller matrices — a compressed matrix (half the values of the dense representation) and a matrix with 2-bit indices, indicating the positions of the matrix elements in the dense matrix to be multiplied with those on the compressed matrix. To use the 2:4 fine-grained sparsity format, there must exist at least two zeros in each set of four contiguous values in any given matrix row (row-major representation). Notice that the use of this format is a strict requirement to enable using the sparse tensor cores.

The matrices are represented relying on the use of the 16-bit IEEE-754 floating-point (half) or the 32-bit IEEE-754 floating-point (float) numerical formats. Using cuBLAS, we evaluate the use of uniform-precision GEMM operation (on CUDA cores) and that of mixed-precision GEMM using 16-bit inputs with 32-bit accumulation (on CUDA cores and on Tensor cores). On cuSPARSE SpMM, we evaluate the use of the COO, CSR and CSR formats using uniform 32-bit precision. When using the (dense) tensor cores on cuSPARSE SpMM, which relies on the Blocked-ELL format, 16/32 mixed-precision is used. Finally, when using CUTLASS to make use of the sparse tensor cores, we also rely on mixed-precision with 16-bit inputs and 32-bit accumulation. Notice that direct operation with 32-bit data is not supported in tensor cores (either dense or sparse). When using 16-bit precision inputs we always rely on 32-bit accumulation (i.e. mixed precision), since that is most representative of real use cases. As a matter of fact, cuSPARSE does not support uniform 16-bit precision SpMM for the COO, CSC, CSR formats.

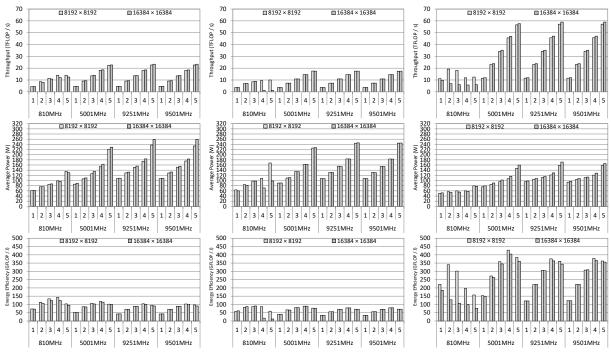

#### 3.1.2 GEMM ON CUDA CORES AND ON TENSOR CORES

Fig. 36 depicts the throughput, power and energy efficiency achieved with different pairings of core and memory frequencies, for GEMM runs (M,N,K set to 8192 or 16384) using the cuBLAS library. Fig. 36(a) and Fig. 36(b) show these metrics for the use of 16-bit and 32-bit precision inputs on CUDA cores. The same metrics are showcased in Fig. 36(c) for the use of 16-bit precision inputs on tensor cores.

The achieved results indicated that close to the full potential of the cuBLAS GEMM kernels is being achieved, with no significant difference in the throughput achieved (TOPS/s) for processing matrices with 8192 × 8192 or 16384 × 16384 elements. Execution relying on cuBLAS uniform-precision 32-bit GEMM on CUDA cores achieved up to 23.368 TFLOP/s, which represents 78.50% of the vendor-announced throughput (29.77). Mixed-precision cuBLAS GEMM on CUDA cores resulted in worse throughput, achieving only 17.44 TFLOP/s. This can be attributed to the execution of more instructions, since mixed-precision is not natively supported in CUDA cores.

Higher throughput on CUDA cores (29.49 TFLOP/s, 99.07% of peak) has been achieved with uniform-precision 16-bit operation, i.e. 16-bit inputs and 16-bit accumulation (not represented in the charts). However, since this is not safe to use for many applications and not supported in several libraries (e.g. not supported in COO, CSC and CSR on cuSPARSE), uniform-precision 16-bit operation has not been included as part of the main experimental campaign.

Operation using tensor cores allowed to achieve a significantly higher throughput (up to 58.96), which represents 99.03% of the peak (59.54) at the used precision, i.e. 16-bit inputs with 32-bit accumulation. This is to expect, since tensor cores are hardware units especially designed for performing matrix multiplication operations at high throughput.

The reported average power consumption is comparable between uniform precision and

(a) Uniform-precision 32-bit GEMM on (b) Mixed-precision 16/32-bit GEMM on (c) Mixed-precision 16/32-bit on tensor CUDA cores. CUDA cores.

**Figure 36** Throughput, power and energy efficiency for cuBLAS GEMM with different GPU core (1: 345MHz, 2: 690MHz, 3: 1020MHz, 3: 1365MHz or 5: 1710MHz) and memory (810MHz, 5001MHz, 9251MHz or 9501MHz) frequencies, with input matrices of size  $8192 \times 8192$  or  $16384 \times 16384$  elements.

mixed-precision matrix multiplication on CUDA cores, 258.10W or 245.10W for processing  $16384 \times 16384$  matrices at the highest clock/memory frequencies. However, the use of tensor cores, for the same core/memory frequencies, results in a much lower power consumption (165.88) than if relying on CUDA cores for the GEMM computations. This can be attributed to the specialization of these special-purpose acceleration units for the task at hand, since tensor cores are built for the sole purpose of multiplying matrices.

As expected, throughput is at its highest when pairing the highest GPU core and memory frequencies considered. However, depending on the metric(s) one wants to optimize, there are benefits in using lower GPU core and/or memory frequencies. The fact that, overall, throughput is significantly affected when using lower core frequencies (and not lower memory frequencies) can be attributed to the compute-bound nature of GEMM computations.

Core frequency variation resulted in a more significant impact on power consumption than memory frequency variation. Lowering the core frequency results in a drop in voltage, resulting in a drop in power consumption. This is especially the case when dropping from 1710MHz to 1365MHz, as the higher is the frequency a chip is operating at, the less efficient it becomes.

Dialing back the memory frequency can be useful for the resulting power consumption reduction; especially because it could often be performed with a negligible impact on performance. As a matter of fact, using a memory frequency of 5001MHz (52.64% of the maximum) is enough to sustain close to peak performance for all considered core core frequencies. Memory frequency only has a very noticeable impact on throughput when set to its lowest considered value (810MHz). This is to expect since at such point GEMM operations become memory bound.

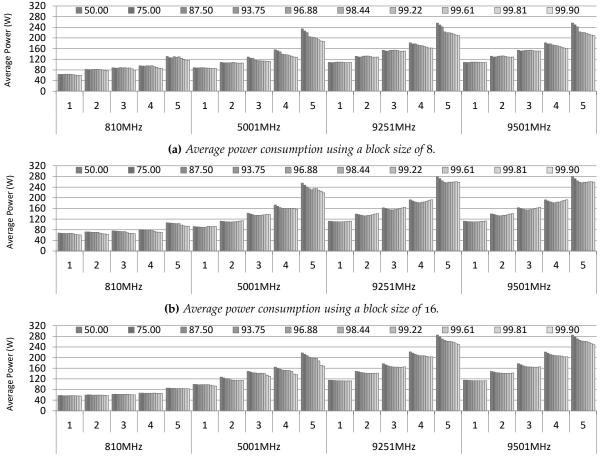

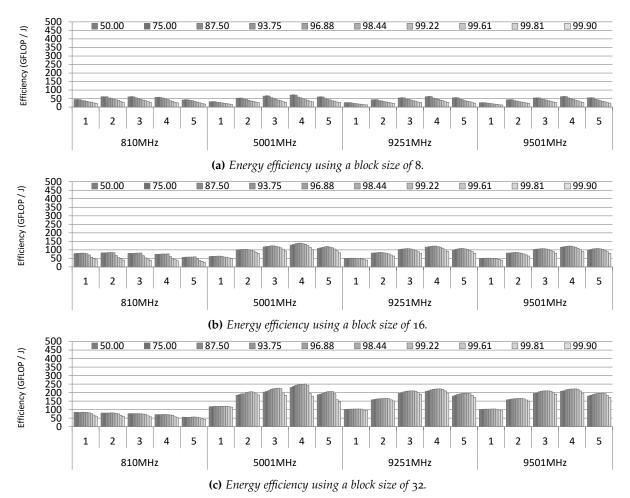

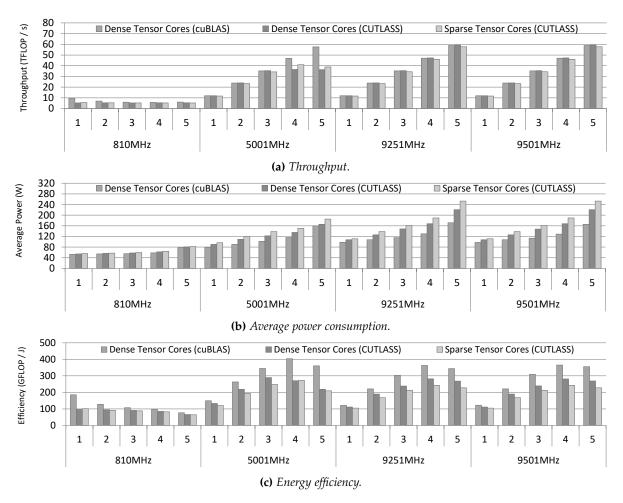

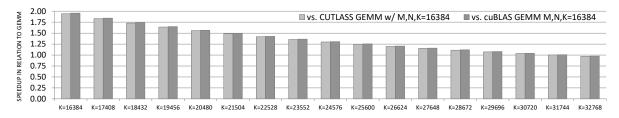

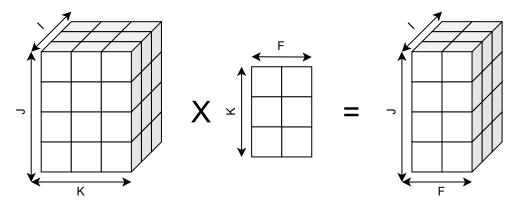

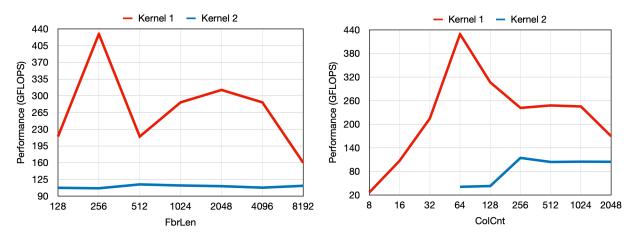

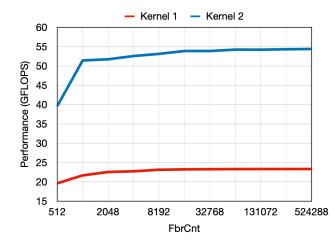

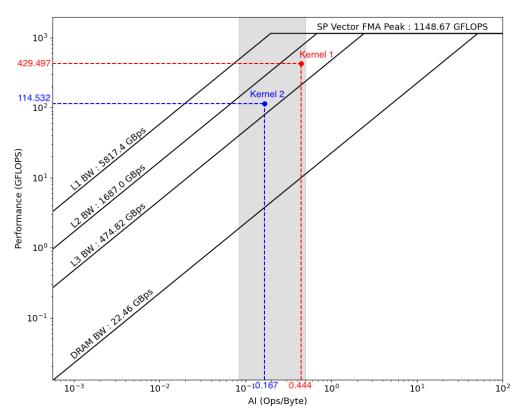

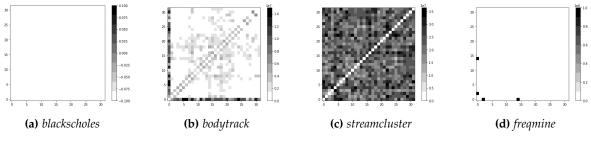

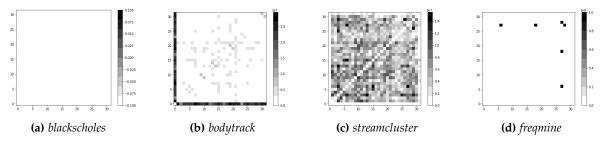

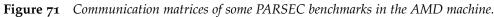

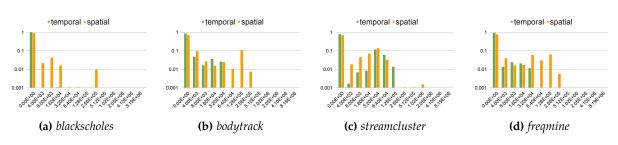

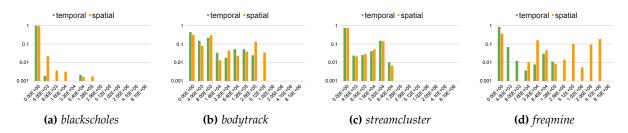

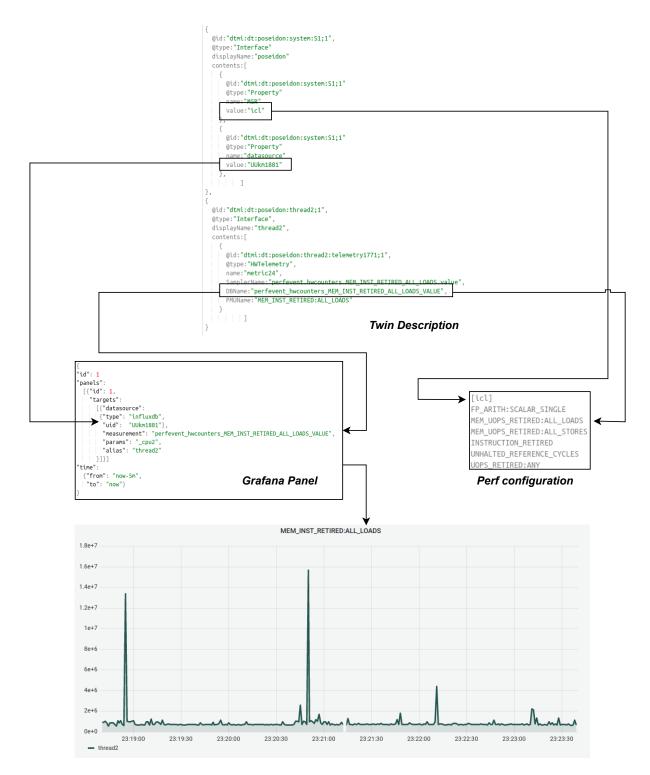

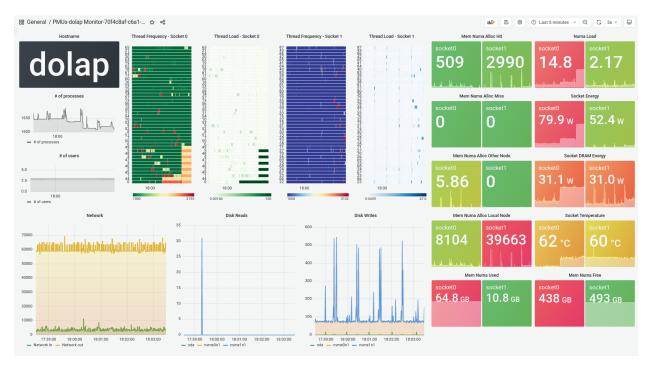

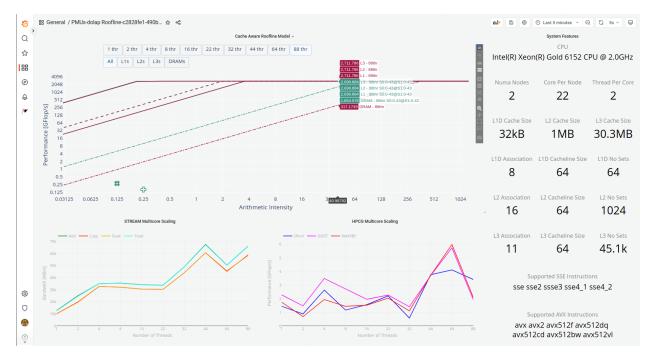

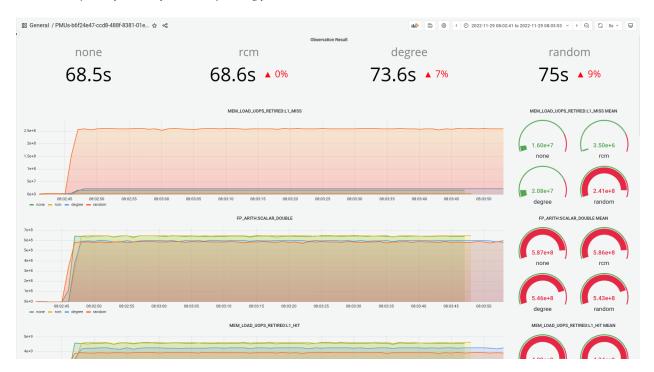

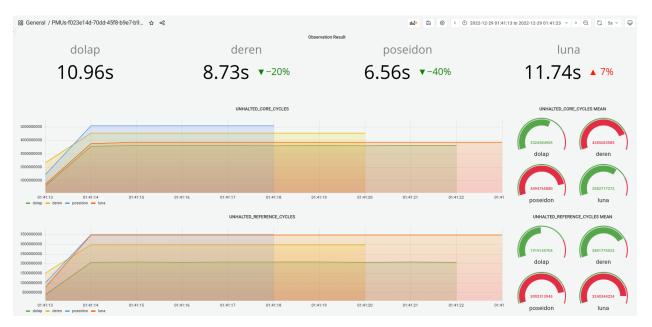

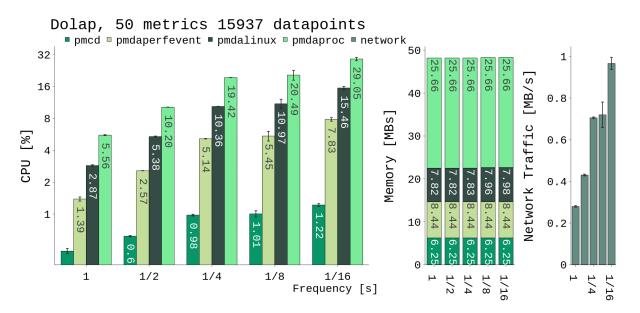

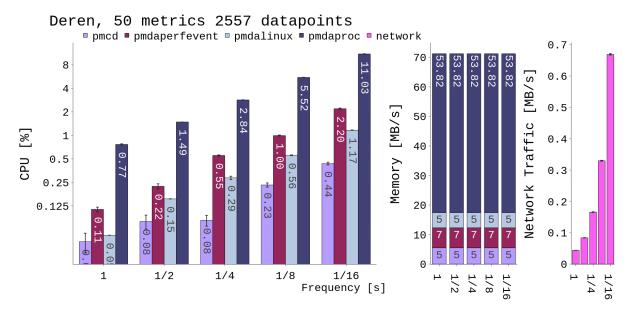

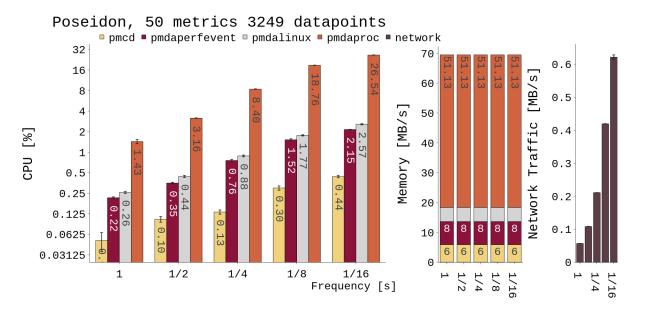

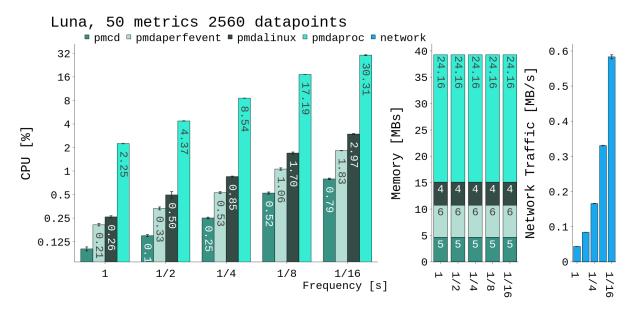

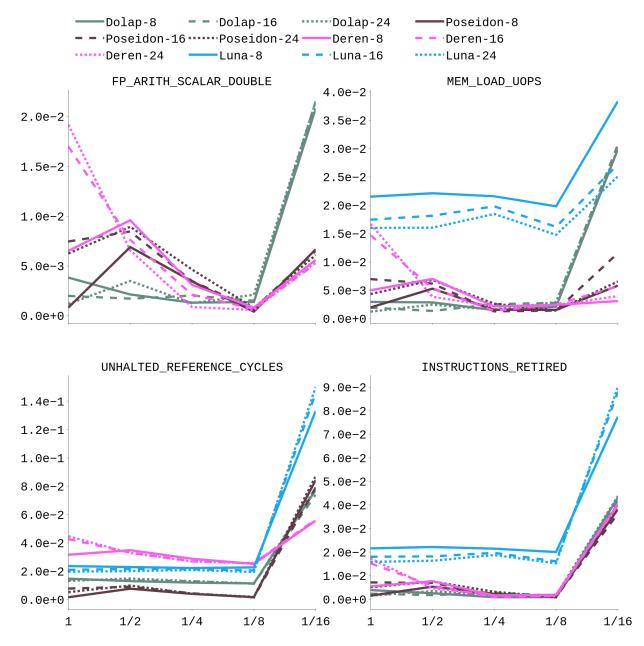

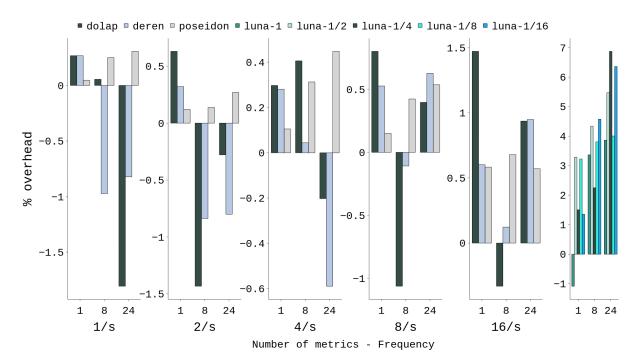

Notice that these trends can be observed for all three considered execution modes. While